9. Анализа на FET засилувач

Анализа на FET засилувач

9.1 Засилувач за CS (и извор на резистори)

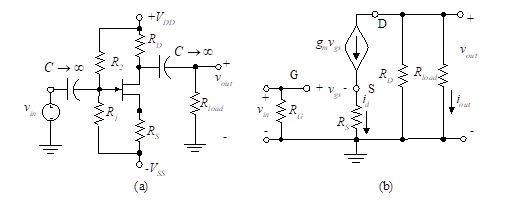

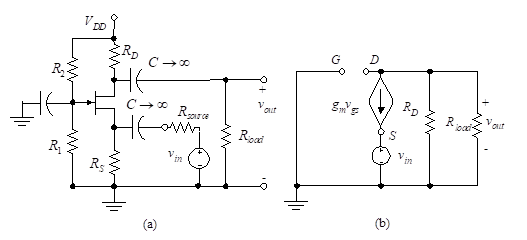

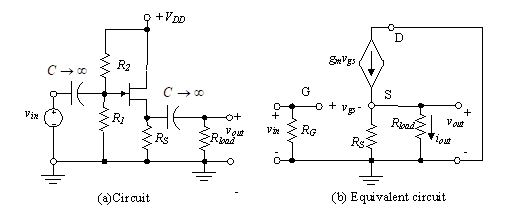

Слика 33 - Засилувач CS со изворен отпорник

Слика 33 (а) го покажува CS засилувачот со изворниот отпорник. На ac еквивалентно коло е на слика 33 (б). Претпоставуваме ro е голем во споредба со, па затоа може да се запостави. Ако кондензатор е присутен помеѓу изворот и земјата (т.е. CS засилувачот), ние треба едноставно да го поставите RS еднаква на нула во следните ac равенки. Ова го правиме на крајот на оваа деривација.

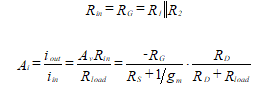

Во дел (б) на Слика 33, RG е паралелна комбинација на R1 R2 VGG е еквивалентниот напон на Thevenin на пристрасното коло:

(41)

(41)

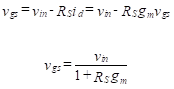

Да се анализира ac еквивалентно коло, ние пишуваме равенка на КВЛ околу цевката на портата.

(42)

(42)

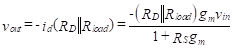

Излезниот напон, vнадвор, е дадена од

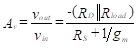

Напонот се зголемува, Av, сега е пронајден.

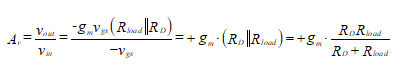

(43)

(43)

Ако изворот отпор, RS, се заобиколува со кондензатор, дозволуваме RS = 0, и зголемувањето на напонот се зголемува до

![]() (44)

(44)

Ова е обично голем негативен број.

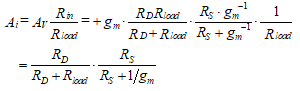

Влезниот отпор и тековната добивка се дадени од

(45)

(45)

9.2 Засилувач на CG

Слика 37 (а) го покажува едностепен заеднички-засилувач и Слика 6.37 (b) го покажува својот ac еквивалентно. Уште еднаш сме запоставени ro под претпоставка дека е голема во споредба со паралелната комбинација на RD со Rоптоварување.

Слика 37 - CG засилувач

Од Слика 37 (б) левиот циклус, напонот од портата до извор е даден од

![]() (46)

(46)

Тековната преку RS is

(47)

(47)

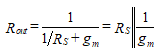

така што (влезот) отпор кој го гледа изворот е

![]() (48)

(48)

Ова треба да се спореди со равенката (45) за CS засилувачот. Гледаме дека ако отпорноста на портата е висока, влезниот отпор на засилувачот со заеднички извор може да биде многу поголем од оној на common-gate засилувачот. Всушност, бројот на апликации на CG засилувачот е ограничен поради ниската влезна импеданса.

Напонот се добива од

(49)

(49)

Споредувајќи го ова со Equation (44), можеме да видиме дека зголемувањето на напонот за CS засилувачот со непрекинато отпор во изворното коло е исто што и оној на CG засилувачот, освен ако CG засилувачот не ја префрли фазата.

Излезниот отпор едноставно е даден од RD (ставете тест проток и мерете го напонот додека го поставувате vin до нула).

Тековната добивка на CG засилувачот е

(50)

(50)

9.3 Засилувач на CD (SF)

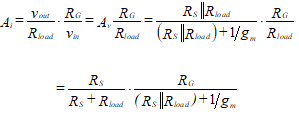

Слика 39 (а) го прикажува засилувачот за единечен фазен извор (СФ) и Слика 39 (b) го покажува својот ac еквивалентно. Како и кај секоја конфигурација што ја анализиравме, го изоставиме големиот отпор, ro под претпоставка дека е многу поголема од паралелната комбинација на RS со Rоптоварување.

Слика 39 - ЦД засилувач

Влезниот отпор е едноставно Rin = RG. Пишувајќи ја равенката KVL околу јамката од порта до извор, имаме

![]() (51)

(51)

од кои добиваме

![]() (52)

(52)

Излезниот напон е

![]() (53)

(53)

Напонот добива е односот на излезот на влезниот напон.

![]() (54)

(54)

Имајте на ум дека ова зголемување на напонот е помало од единство, и се приближува на една како паралелна комбинација на RS со Rоптоварување се зголемува.

Сега ја наоѓаме моменталната добивка. Излезната струја е соодносот на излезен напон со отпорноста на оптоварување. Влезната струја е влезниот напон поделен со RG. Затоа добивката е дадена од

(55)

(55)

Излезот отпор може да се најде со замена на отпорност на оптоварување со тест напон, vтест, а потоа наоѓање на добиената струја, iтест. Текот управуван од овој тест извор се наоѓа од една јазонска равенка на изворот.

![]() (56)

(56)

Напонот од извор до извор е едноставно -vтест бидејќи претпоставуваме дека влезниот напон е нула. Оттука, излезниот отпор е

(57)

(57)

АКТУЕЛНО - 9. Анализа на засилувачот FET

АКТУЕЛНО - 9. Анализа на засилувачот FET ПРЕТХОДНИ- 8. Засилувачи на FET - Канонски конфигурации

ПРЕТХОДНИ- 8. Засилувачи на FET - Канонски конфигурации