5. Интегрирани кола MOSFET

Интегрирани кола MOSFET

Кога MOSFET транзисторите се фабрикувани како дел од интегрирано коло, практичните размислувања бараат две големи промени во конфигурациите на колото. Прво, големите кондензатори за спојување и бајпас што се користат во дискретни засилувачи практично не можат да се фабрикуваат во интегрираните кола поради малата големина. Овој недостаток го опфаќаме со фабрикување на директно засилени засилувачи.

Втората голема промена е дека не можеме лесно да ги измислиме резисторите што се користат како дел од колективното коло. Наместо тоа, ние ги користиме активните оптоварувања и тековните извори составени од MOS транзистори.

Интегрираните кола ги користат и NMOS и PMOS колото. CMOS е почеста во дигиталните кола, додека NMOS обично се користи за IC диоди со поголема густина (т.е. повеќе функции по чип).

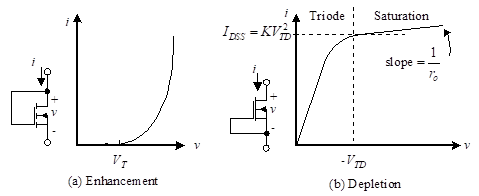

Симулацијата на активните товари ги искористува наклонот на карактеристичните кривини на MOS. Слика 23 покажува два типа на активни товари. На Слика 23 (а), ние прикажуваме оптоварување за подобрување на NMOS, додека 23 (b) покажува оптоварување на NMOS-осипување. Исто така прикажани на сликата се релевантните карактеристични криви.

Слика 23 - активни товари

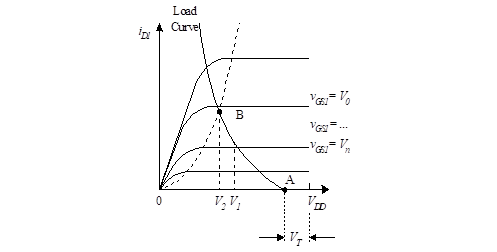

За оптоварувањето за зголемување на NMOS, односот помеѓу напонот и струјата е даден со

![]()

(29)

Еквивалентен отпор на оваа конфигурација е 1 /gm, каде што вредноста на транспроводноста е онаа што се применува на точката на пристрасност.

Намаленото оптоварување на NMOS има еквивалентен отпор кој се одредува со наклонот на карактеристиката дадена со следнава равенка

(30)

5.1 Стиснување на MOSFET интегрирани кола

Сега, кога имаме две техники за симулирање на активни товари, можеме да се осврнеме на проблемот со тенденција. Ние го користиме активното оптоварување на местото на отпорноста на оптоварување во некоја од колажните конфигурации. За да ја покажеме техниката за анализа на овие, да го разгледаме NMOS засилувачот користејќи оптоварување за подобрување, како што е прикажано на Слика 24.

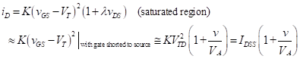

Транзистор етикетиран Q2 заменува RD на нашите претходни кола. За да ја одредиме работната точка на мирување, ги користиме истите техники како што правевме во Дел 4, „Конфигурации и пристрасност на засилувачот на FET“, само заменувајќи ја графичката карактеристика на оптоварувањето на подобрувањето за линијата на оптоварување на отпорот. Тоа е, ние треба да го најдеме истовременото решение на FET транзисторните карактеристики со равенката за товарната линија. Ова можеме да го направиме графички како што е прикажано на слика 25.

Параметричните кривини се карактеристични криви за засилувачкиот транзистор, Q1. Напонот наспроти тековната карактеристика на активното оптоварување, Q2 се оние на Слика 23. Излезниот напон, vнадвор, е разликата помеѓу VDD и напонот преку активното оптоварување. Струјата во активното оптоварување е иста како и струја на мозоци во засилувачкиот транзистор. Затоа ја конструираме оптоварувачката линија со преземање на префрлената огледална слика на карактеристиката на Слика 23. Оперативната точка е пресекот на оваа крива со соодветната крива на карактеристиките на транзисторот. Треба да го најдеме напонот од портата до извор за да знаеме која транзисторна крива треба да ја изберете. Како што ќе видиме следно, влезниот пристрасен напон често се заменува со активен извор на струја.

Слика 25 - Графичко решение за Q-точката

Сега кога знаеме како да симулираме активно оптоварување, го свртуваме вниманието кон генерирањето на референтната струја која треба да се користи како дел од колото за влез пристрасност. Овие тековни извори се користат на ист начин како што ги користевме за прибирање на BJT засилувачите.

Слика 26 - Тековно огледало

Ние анализираме MOSFET тековната огледало. Тековното огледало е прикажано на Слика 26. Се претпоставува дека двата транзистори совршено се исти. Излезната струја е струјата на одводот Q2, и референтни струјни дискови Q1. Ако транзисторите се совршено совпаднати, излезната струја точно ќе се изедначи со референтната струја. Ова е точно бидејќи транзисторите се поврзани паралелно. Исто како што беше случај со огледалото на струјата BJT, референтната струја може да се генерира со примена на референтен напон преку референтниот отпор, како што е прикажано на слика 26 (б).

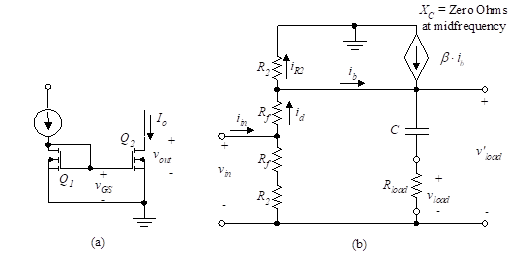

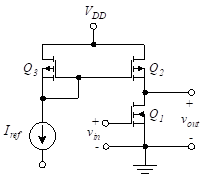

Ставањето на разните потцрузи заедно (т.е. активното оптоварување и референтната струја) резултира со CMOS засилувач на Слика 27.

Зголемувањето на овој засилувач е дадено од

![]()

(31)

Слика 27 - CMOS засилувач

5.2 ефект на телото

Нашата дискусија за Дел „2. Полупроводник метал-оксид FET (MOSFET) ”се однесува на подлогата (или телото) на MOSFET. Овој супстрат игра важна улога во воспоставувањето на каналот. Во работата на дискретни МОСФЕТ, телото е често поврзано со изворот на енергија. Во такви случаи, подлогата нема директно влијание врз работата на уредот и се применуваат кривините развиени порано во ова поглавје.

Ситуацијата се менува кога MOSFETs се фабрикувани како дел од интегрираните кола. Во такви случаи, подлогата на секој поединечен транзистор не е изолирана од други подлоги. Навистина, подлогата често се дели меѓу сите MOSFETs на чип. Во PMOS IC, споделената подлога ќе биде поврзана со најпозитивниот извор терминал, додека во NMOS таа е поврзана со земјата (или со негативно снабдување ако е присутна). Ова воспоставува обратна предрасуда помеѓу изворот и телото на секој транзистор. Ефектот на оваа обратна пристрасност е да се променат оперативните карактеристики. На пример, во n-канал уред, тој ефективно го зголемува прагот (VT). Износот за кој се менува прагот зависи од физичките параметри и конструкцијата на уредот. За NMOS, оваа промена може да се приближи до

![]()

(32)

Во равенката (32), γ е параметар на уред кој варира помеѓу околу 0.3 и 1 (V-1 / 2). VSB е напон од извор до тело и е Ферми потенцијал. Ова е својство на материјалот, а типична вредност е 0.3 V за силикон.

АКТУЕЛНО - 5. Интегрирани кола MOSFET

АКТУЕЛНО - 5. Интегрирани кола MOSFET ПРЕТХОДНО-4. FET Засилувачи Конфигурации и Погодување

ПРЕТХОДНО-4. FET Засилувачи Конфигурации и Погодување