11. Beste gailu batzuk

Beste gailu batzuk

Atal honetan aurkezten dira bi eta hiru terminaletako gailu normalen ondorio diren beste gailu batzuk.

11.1 Metal Semiconductor Barrier Junction transistor

The erdieroale metalikoen hesi baterako transistorea (MESFET) FET baten antzekoa da, bidegurutzea erdieroale metalikoa da, Schottky diodoekin gertatzen den moduan. Silizioa (Si) edo gálio arsenidoa (GaAs) egina dauden FETak ateak zabaltzen diren edo ioi inplantatuekin egiten dira. Hala ere, badira abantailak Schottky barrera metalikodun atea erabiltzea kanalean n-mota motako eta kanal zabalera laburrak behar dira. Galio artsenuroa (GaAs) lantzeko zaila da, hala ere Schottky-ko oztopo onak egiten ditu, maiztasun handiko aplikazioetan baliagarriak baitira elektroiak GaAs-n Si-n baino azkarrago ibiltzen direlako. MESFETetan GaAs erabiltzeak mikrouhin aplikazioetan errendimendu ona erakusten duen transistorea lortzen du. Siliziozko transistore bipolarraren aldean, GaAs MESFETek 4 GHz baino gehiagoko sarrerako maiztasunetan errendimendu hobea dute. MESFET hauek irabazi handia, zarata txikia, eraginkortasun handia, sarrerako inpedantzia handia eta ihesaldi termikoa eragozten duten propietateak erakusten dituzte. Mikrouhin osziladoreetan, anplifikadoreetan, nahasgailuetan eta abiadura handiko kommutazioetan ere erabiltzen dira. GaAs MESFETak maiztasun handiko aplikazioetarako erabiltzen dira.

11.2 VMOSFET (VMOS)

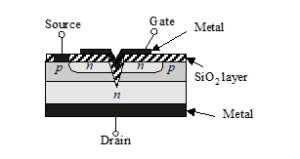

Egoera solidoko gailuen potentzia ahalmena handitzeko ikerketa ahalegin handia egin da. Itxaropen handia erakutsi duen eremua MOSFET da, non eroapen kanala aldatu egiten den iturri-drainatze ohiko lerroa baino "V" bat eratzeko. Geruza erdieroale gehigarri bat gehitzen da. Terminoa VMOS iturria eta ihesa arteko korrontea eraikuntza ondorioz bide bertikal bat jarraitzen du. Drainatzea orain erdieroale erantsi baten zatian kokatzen da, 47 irudian erakusten den bezala. Honek transistoreen drainatze gunea jartzeko aukera ematen du kontaktuan jarriko den bero-konketa batekin, gailuan sortutako beroa xahutzeko. V formako atea bi MOSFET bertikalak kontrolatzen ditu, koadroaren albo bakoitzean. Bi S terminalak paralelismoa erabiliz, uneko ahalmena bikoiztu egin daiteke. VMOS ez da simetrikoa, beraz S eta D terminalak ezin dira elkar trukatu, energia txikiko MOS FET kasuetan gertatzen den moduan. FET konbentzionalak miliamperen ordena korronteak mugatzen dira, baina VMOS FETak 100A uneko gama erabiltzeko erabil daitezke. Horri esker, FET konbentzionalaren gaineko hobekuntza handia da.

VMOS gailuak maiztasun handiko eta potentzia handiko aplikazioen konponbidea eman dezake. Hamar watt gailuek UHF beheko maiztasun handiko banden maiztasunetan garatu dituzte. VMOS FETen abantaila garrantzitsuak daude. Tenperatura koefiziente negatiboa dute iheslariak saihesteko. Halaber, isurketa txikiko korrontea erakusten dute. Aldaketa abiadura altuak lortzeko gai dira. VMOS transistoreek bere kurben ezaugarrien arteko tarte berdina izan dezakete atearen tentsioaren gehikuntza berdinak lortzeko; beraz, potentzia handiko lineako anplifikadoreentzako biteko zurtoin transistore bezala erabil daitezke.

47 irudia - VMOS eraikuntza

11.3 Beste MOS gailuak

Beste MOS gailu mota bat da bikoiztuko prozesua FET fabrikatu da batzuetan deitzen zaio DMOS. Gailu honek kanalen luzera txikiagotzeko abantaila du, eta horrela, energia gutxiko xahutzea eta abiadura handiko gaitasuna eskaintzen ditu.

Batzuetan aipatzen da, batzuetan, zementu-substratu batean dagoen silizio uharte txikietan fabrikatzea SOS. Silizio uharteak zafiroaren substratuan hazitako siliziozko geruza finaren ondorioz sortzen dira. Fabrikazio mota honek silizio uhartearen artean isolamendua eskaintzen du eta, horrela, gailuen arteko parasitoen gaitasun handia murrizten du.

MOS teknologiak abantaila du kondentsadoreak eta erresistentziak (MOSFET erabiliz) FET-rekin batera egiten direla, nahiz eta balio handiko kondentsadoreak ez dira bideragarriak. Osagarri MOSFET bat erabiliz, bi terminaleko erresistentzia egiten da eta ihesari loturiko MOSFET atea eragiten du FET-a pinch-offean funtzionatzea. MOSFET atea drainatzearekin lotuta dago, FET eragin dezakeen iturri baten bidez. Bertan, ezaugarriak dituen tentsio kontrolatutako erresistentzia eskualdean funtzionatuko du. Horrela, ihesa-kargatzeko erresistentziak MOSFET batek ordeztuko ditu, horregatik txip area aurrezten duena.

LABURPENA

Kapitulu honen helburua eremuaren efektuko transistoreen anplifikadorearen zirkuituen analisia eta diseinua aurkeztea zen. FET oso desberdina da BJTrekin. Bere funtzionamendua uneko kontrolatutako gailua den BJTrekin alderatuta dagoen tentsio batek kontrolatzen du.

Gure hurbilketa BJTren kapituluekin paraleloki dago. FET portaera gobernatzen duten fenomeno fisikoen azterketa batekin hasi ginen. Prozesuan, FET eta BJTen arteko kontrastea azpimarratu genuen. MOSFETekin ikerketa hasi ginen eta gero JFET-ekin arreta jarri genuen. Gailu garrantzitsu hauetarako seinale txiki ereduak ere garatu genituen. Eredu horiek FET anplifikadoreen hainbat konfigurazio aztertzeko erabili genituen. FET zirkuituak aztertzean, diseinuan arreta jarri genuen zehaztapenak betetzeko. Simulazio informatikoen programek erabiltzen dituzten ereduak ere aztertu ditugu.

Laburbilduz, FETek nola integratzen diren aztertu dugu zirkuitu integratuen barruan. Kapitulu hau beste FET gailu batzuetarako sarrera batekin amaitu zen, MESFET eta VMOS barne.

GAUR EGUNGO - 11. Beste gailu batzuk

GAUR EGUNGO - 11. Beste gailu batzuk AURREKOA- EZAZU. FET anplifikadorearen diseinua

AURREKOA- EZAZU. FET anplifikadorearen diseinua