2. Metal-oxido Semiconductor FET (MOSFET)

Metal-oxido Semiconductor FET (MOSFET)

Metalo-oxidoaren erdieroale FET (MOSFET) lau terminal gailu bat da. Terminalak dira iturria (S), atea (G) ihesa (D). The substratuaren or gorputza laugarren terminala osatzen du. MOSFET kanaletik isolatutako dioxido dielektriko batekin isolatuta dagoen atea terminalarekin egina dago. MOSFETek ere izan daitezke agortzea or hobekuntza modua. Handik gutxira, bi termino hauek definitzen ditugu.

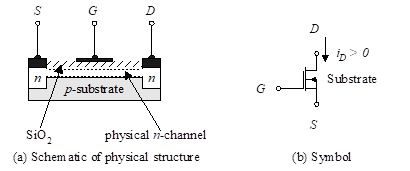

1 irudia - n-kanal agortzea MOSFET

MOSFET batzuetan IGFET gisa aipatzen dira (isolatutako ate-eremu efektuko transistoreak) SiO dela eta.2 atea eta substratua arteko isolatzaile gisa erabilitako geruza. Gure azterketa agortu egiten dugu MOSFET moduan. BJTak ere bai NPN or PNPMOSFETek bai izan daitezke n-channel (NMOS) edo p-channel (PMOS). 1 irudia baten egitura fisikoa eta sinboloa erakusten du n-kanalaren agortzea MOSFET. Kontuan izan substratua iturburu terminalera konektatuta dagoela. Hau izango da ia beti.

Agortzea MOSFET da fisiko ihesa eta iturriaren artean sartutako kanala. Ondorioz, tentsio bat denean, vDS, ihesa eta iturria, korronte bat artean aplikatzen da. iD, ihesa eta iturria artean badago, nahiz eta atea terminal G ez dago lotutavGS = X V).

Eraikuntza n-kanalaren agortzea MOSFET hasten da psilizio zilindroa. The n-Doped iturri eta ihesa putzuak erresistentzia txikiko konexioak osatzen du n-channel, 1 irudian erakusten den bezala. Silizio dioxidoaren geruza mehe bat jartzen da iturriaren eta drainatzearen arteko eremua estaltzen. SiOa2 isolatzaile bat da. Silizio dioxidoaren isolatzaile isolatzailean aluminiozko geruza bat metatzen da atearen terminala osatzeko. Funtzionamenduan, negatiboa vGS elektroiak kanalaren eskualdetik ateratzen ditu eta, ondorioz, kanala apurtuz. Noiz vGS tentsio jakin bat lortzen du VT, kanala da atzaparretuta. Balio positiboak vGS handitu kanalaren tamaina, drainatze-korrontea areagotuz. Agortze MOSFETrek balio positiboak edo negatiboak izan ditzake vGS. Atea kanaletik isolatuta dagoenez, atea unekoa oso txikia da (10en eskaeran)-12 A).

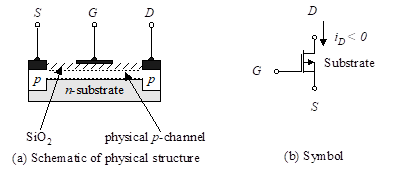

2 irudia - p kanal agortzea MOSFET

2 irudia 1 Irudiaren antzekoa da, baina hori aldatu dugu n-kanalaren agortzea MOSFET bati p-kanalaren agortzea MOSFET.

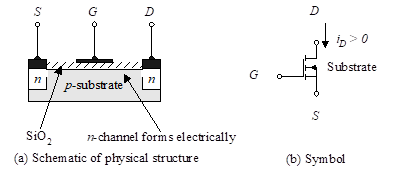

The n-kanalaren hobekuntza MOSFET 3 irudian erakusten da zirkuituaren sinboloarekin batera. Hau eremu-efektuko transistoreen ohikoena da.

3 irudia - n-kanalaren hobekuntza MOSFET

The n-kanalaren hobekuntza MOSFET-a agortzearen MOSFET ezberdina da n-layer. Kanal bat ezartzeko atea eta iturria arteko tentsio positiboa eskatzen du. Kanal hau ate-iturri positiboaren tentsioaren ekintza da. vGS, hau da, substratuaren eskualdeko elektroiak erakartzen dituena nihesa eta iturria. positiboa vGS elektroiek oxido geruzaren azpian azalera metatu egiten dute. Tentsioa atalasea iristen denean, VTeskualde honetara elektroi kopuru nahikoa erakartzen dute errealitate gisa joka dezan n-channel. Ez dago drainatze-korrontea. iD existitzen den arte vGS gainditzen VT.

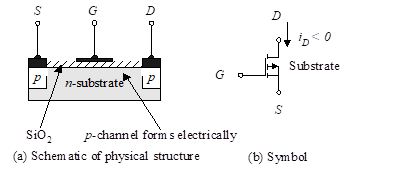

4 irudia 3 Irudiaren antzekoa da, baina hori aldatu dugu n-kanalaren hobekuntza MOSFET a p-kanalaren hobekuntza MOSFET.

4 irudia - p kanalaren hobekuntza MOSFET

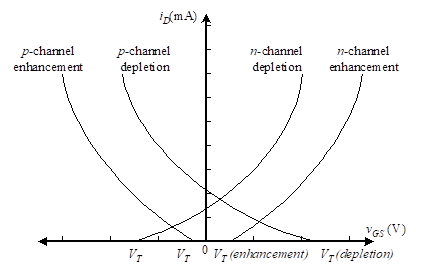

Laburpen gisa, MOSFET familiak identifikazioa erakusten du iD versus vGS 5 irudian erakusten diren kurbak. Ezaugarri kurba bakoitzak nahikoa drainatze-iturri tentsioarekin garatzen da vDS gailua funtzionamendu normalaren eskualdean mantentzeko iD versus vDS kurba. Hurrengo atalen eztabaidak atalase tentsioa zehazten du VT bai hobekuntza MOSFET eta agortzea MOSFET.

5. irudia - iD versus vGS MOSFET familiaren ezaugarriak nahikoa iturri tentsio iturri VDS

2.1 Hobekuntza-modua MOSFET terminalaren ezaugarriak

MOSFETen funtzionamendurako oinarrizko egitura eta oinarriak aurkeztu ditugunean, ikuspegi bat erabiltzen dugu hobekuntza moduan gailuaren terminalaren portaera aztertzeko. Egin ditzagun lehenik 1. Irudian zenbait ohar orokor. Pentsa ezazu MOSFETeko korrontearen fluxu normala hustubidetik iturriraino (BJTn bezala, kolektore eta igorlearen artean dago). -Rekin gertatzen den bezala NPN BJT, atzera-bizkarreko bi diodoak ihesa eta iturri artean daude. Hori dela eta, kanpoko tentsioak atea aplikatu behar diegu, korrontea isurketaren eta iturriaren arteko korrontea ahalbidetzeko.

Iturria lurperatzen badugu eta ateari tentsio positiboa aplikatzen badiogu, tentsio hori atea-iturriaren tentsioa modu eraginkorrean dago. Atal tentsio positiboak elektroiak erakartzen ditu eta zuloak uxatzen ditu. Tentsioa atalasea gainditzen dueneanVT), nahikoa elektroi erakartzen dira drainatze eta iturriaren artean eramateko kanal bat eratzeko. Une honetan transistorea aktibatzen da eta unekoa bietako funtzioa da vGS vDS. Argi dago hori VT zenbaki positiboa da n-kanal gailua eta zenbaki negatiboa p-kanal gailua.

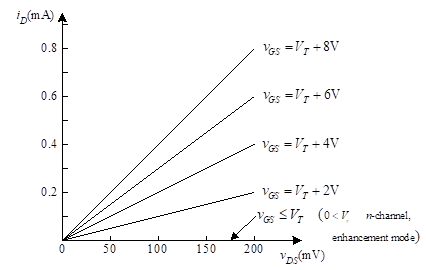

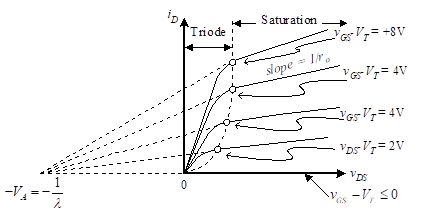

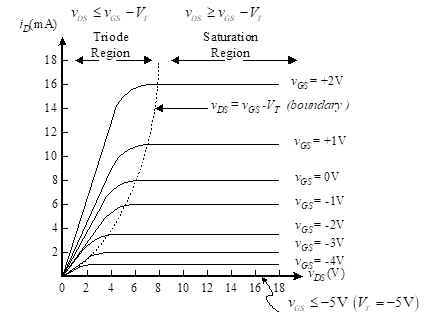

Kanala sortu ondoren (hau da, vGS >VT), korronte horren fluxua drainatze eta iturriaren artean egon daiteke. Uneko fluxuaren araberakoa da vDS, baina baita ere araberakoa vGS. Noiz vGS apenas atalasea gainditzen duena, korronteak oso gutxi ditzake. As vGS Atalasea gainditzen du, kanalak eramaile gehiago ditu eta korronte handiagoak posible dira. 6 irudia arteko erlazioa erakusten du iD vDS non vGS parametroa da. Kontuan izan vGS atalasea baino txikiagoa, egungo fluxurik gabe. Goi mailako vGS, arteko harremana iD vDS gutxi gorabehera lineala da, MOSFETrek erresistentziaren araberakoa duen erresistentzia bezala jokatzen duela vGS.

6 irudia -iD versus vDS hobekuntza moduan n-kanala MOSFET denean vDS txikia da

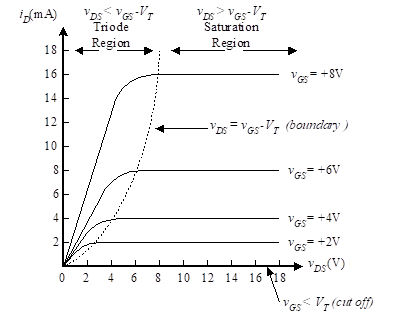

6 irudiko kurbak lerro zuzenak dira. Hala ere, ez dira lerro zuzen gisa jarraituko vDS handitzen da. Gogoratu ate positiboaren tentsioa eroankortasun kanala sortzeko erabiltzen dela. Hau egiten du elektroiak erakarrita. Drainatze tentsio positiboa gauza bera egiten ari da. Kanalaren drainatze amaierara hurbiltzen den bitartean, kanala sortzen duen tentsioa hurbiltzen da vGS-vDS bi iturriek elkarren aurka egiten baitute. Aldea hau baino gutxiago bada VT, kanala jada ez da existitzen iturri eta ihesa arteko espazio osoarentzat. Kanala da mugatutako drainatze amaieran, eta gehiago handitzen vDS ez dute eraginik handituko iD. Hau eragiketa normalaren edo normala den eremua da saturazioa 7 irudian erakutsitako eskualdea kurba ezaugarrien atal horizontalaren arabera. Aldea baino handiagoa denean VT, hau deitzen diogu triode modua, hiru terminaletan potentziala indarrean eragiten baitu unekoa.

Aurreko eztabaidak 7 irudiaren eragile kurbak eramaten ditu.

7 irudia -iD versus vGS hobekuntzarako modua MOSFET

Eragiketa triodoaren eta funtzionamendu normalaren eskualdearen arteko trantsizioa (saturazioaren eskualdea eta maiz aparkaleku moduan eragiketa moduan identifikatzen dena) arteko trantsizioa XDENDO 7 irudian erakusten da.

![]()

(1)

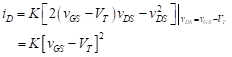

Triodoaren eskualdearen ertzean, kurben belaunak gutxi gorabehera harremanari jarraitzen diote.

![]()

(2)

Ekuazioan (2), K gailu jakin baterako konstante bat da. Bere balioa gailuaren dimentsio eta eraikuntzan erabilitako materialen araberakoa da. Konstantea,

![]()

(3)

Ekuazio honetan, μn elektroi mugikortasuna da; Coxidoa, oxidoaren gaitasunak, atearen unitate bakoitzeko gaitasunaren balioa da; W atearen zabalera da; L atearen luzera da. Ekuazioa erlazio korapilatsu eta lineala adierazten du iD eta bi tentsioak, vDS vGS. Lurrun lineala gutxi gorabehera linealki aldatu nahi dugunez vGS (independentea) vDS), FET ez da triodoaren eskualdean erabiltzen.

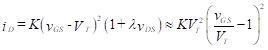

Orain, saturazio eskualdean funtzionatzeko kurba ekuazioa aurkitu nahi dugu. Triodoaren eta saturazio eskualdearen arteko trantsizioaren balioak ezar ditzakegu, trantsizioan (belauna) ekuazioa ebaluatuz (2). Hori da,

(4)

Ekuazio honek drainatze-korrontearen magnitudea zehazten du (8 irudian marratxodun lerroa) atea-iturburuen tentsioaren funtzio gisa. vGS. Beharrezkoa izanez gero, saturazioaren eskualdeko kurba karakterikoen malda arina faktore lineala gehituta jar dezakegu.

![]()

(5)

Ekuazioan (5), λ konstante txikia da (8 irudian agertzen den kurba ezaugarrien atal horizontal hurbileko malda). 0.001 (V.) Baino gutxiago izaten da-1). Ondoren

![]()

(6)

Gure aurreko eztabaida guztia NMOS transistorearekin landu zen. Orain, PMOSen beharrezkoak diren aldaketak aztertuko ditugu. PMOSentzat, balioak vDS negatiboa izango da. Gainera, PMOS kanal bat sortzeko, ![]() .

.

8 irudia - MOSFET transistorearen terminalaren ezaugarriak

NMOS transistoreen ezaugarrietatik aldaketa bakarrak (7 irudia) ardatz horizontalak orain -v daDS + v ordezDS, eta kurba parametrikoak drainatze-korrontea handiagoa adierazten dute, atearen tentsioa gutxitzen denean (NMOS transistorea handitu ordez). Uneko balioen handitze kurbek atari tentsio negatiboagoa izan behar dute. Noiz vGS > VT, transistorea ebaki da. Hobekuntza PMOSerako VT negatiboa da eta PMOS agortzeagatik VT positiboa da.

Uneko triodoaren trantsizioa PMOS transistorearen trantsizioa NMOSenaren berdina da. Hori da,

![]()

(7)

Kontuan izan vGS vDS kantitate negatiboak dira. PMOS transistorean saturazio eskualdearen ekuazioa NMOSen berdina da. Hori da,

(8)

Kontuan izan λ negatiboa da PMOS transistoreentzat kurba aldaketa-tasa geroztik![]() ) negatiboa da.

) negatiboa da.

Ekuazioaren bi aldeetako eratorri partziala hartuz (6) dagokionez vGS, ![]() , lortu dugu

, lortu dugu

![]()

(9)

Nahiago dugu gm konstante izateko, batez ere seinale handiko kulunketarako. Hala ere, baldintza hau gutxi gorabehera seinale txikiko aplikazioetarako FET erabiltzen badugu. Seinale handiko baldintzetan, uhinen distortsioa onargarria izan daiteke aplikazio batzuetan.

2.2 Depletion-Mode MOSFET

Aurreko atalean hobekuntza modua MOSFETrekin landu da. Orain, agiri hau MOSFET moduan kontrastatzen dugu. for the n-kanalaren hobekuntza modua, kanal bat eskuratzeko atalean tentsio positiboa aplikatu behar izan genuen. Tentsio honek nahikoa izan behar du elektroi mugikorren kopuru nahikoa indarrean dagoen kanal batean korronte bat sortzeko.

9 irudia - N-kanal MOSFET agortze modua

En n-kanala agortzeko moduko MOSFET, ez dugu tentsio positibo horren beharrik fisikoki txertatutako kanala baitugu. Horri esker, korrontea hustubide eta iturburu terminalen artean dago atean aplikatutako tentsio negatiboekin ere. Noski, mugan dago atean aplika daitekeen tentsio negatiboaren kopurua oraindik hustubide eta iturriaren artean korronte-fluxua izan bitartean. Muga hori atalase tentsio gisa identifikatzen da berriro, VT. Hobekuntza modutik egindako aldaketaren arabera, atariko iturrirako tentsioa negatiboa edo positiboa izan daiteke, 9. irudian erakusten den moduan.

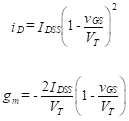

Agortzea modua MOSFET funtzionamendua definitzen duten ekuazioak oso hobekuntza moduaren antzekoak dira. Drainatze-korrontearen balioa vGS zero da IDSS. Hau askotan aipatzen da drainatze-iturria saturazioaren unekoa, Edo zero - ateko hustubide korrontea. Hobekuntza-moduaren MOSFET ekuazioak agortuzko modukoekin alderatzen ditugu

![]()

(10)

Ondoren aurkituko dugu,

(11)

Desplazamendu modua MOSFET formatu diskretuan eskuragarri daude edo zirkuitu integratuetan fabrikatu daitezke hobekuntza moduen motaekin batera. Honek biak barne hartzen ditu p- motaren eta n-mota. Honek zirkuitu diseinatzeko tekniken malgutasun handiagoa ahalbidetzen du.

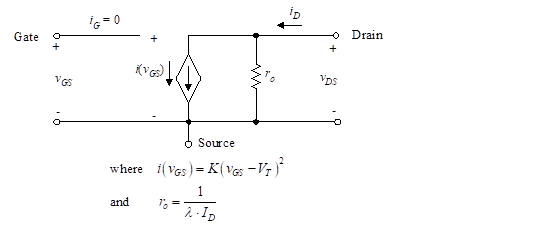

2.3 Seinale handiko zirkuitu baliokidea

Orain, 8 irudiaren [5] (8) edo (XNUMX) seinalearen ezaugarri nagusiak zirkuitu baliokidea garatu nahi ditugu saturazioko eskualdean. Kontuan izan drainatze-korrontea, iD, araberakoa vGS vDS. Atariko iturrirako tentsio konstantea lortzeko, irudiko kurba parametrikoetako batean lan egiten dugu eta erlazioa gutxi gorabehera zuzena da. Korrontearen eta tentsioaren arteko erlazio zuzena erresistentzia baten bidez modelatzen da. Zirkuitu baliokidea, beraz, korronte iturriarekin paraleloan dagoen erresistentziaz osatuta dago, non korronte iturriaren balioak hustubide korrontearen zatia ezartzen duen vGS. Kurbaaren malda araberakoa da vGS. Malda eratorri partziala da

![]()

(12)

non r0 irteerako erresistentzia erresistentzia da. [(5) ekuazioa edo (8) ikusiko dugu erresistentzia hori ematen duena

![]()

(13)

maiuskulak erabiltzen ditugu VGS erresistentzia atea-iturburuen tentsioaren balio konstante jakin baterako definitzen dela adierazteko. Ekuazioaren azken hurbilketa (13) ekuazioa (5) emaitza da λ txikia da. Erresistentzia da, beraz, alderantziz proportzionala biasa uneko, ID. Ondoren, seinale handiko baliokide eredua 11 irudian ematen da r0 ekuazioan garatutakoa da (13).

11 irudia - seinale handiko baliokidea duen zirkuitua

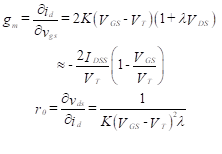

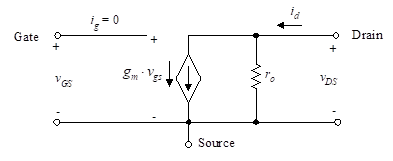

2.4 MOSFET seinale txiki eredua

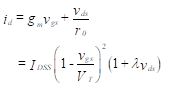

Orain, ondorioz, Ekuazioari lotutako efektu handiak aztertu nahi ditugu. Ekuazio horretan hiru zirkuituaren parametroak: iD, vGS vDS biak dira dc (alborapena) eta ac osagaiak (horregatik erabili dugu adierazpenetan letra xeheen azpian dauden). Interesatuta gaude ac seinale txiki ereduaren osagaiak. Drainatze-korronteak bi tentsioen mende dagoela ikusten dugu, hau da, ate-iturria eta ihesa-iturria. Balio gehikuntzetarako, harreman hori idatzi dezakegu

(14)

Ekuazioan (14), gm is aurrera transcultuctance r0 irteerako erresistentzia da. Beren balioak ekuazioan deribatu partzialak hartzen dituzte (5). Horrela,

(15)

Ekuazioaren hurbilketa (15) ondoriozta behaketatik dator λ txikia bada. Ekuazioa (14) 12 irudiaren seinale txiki ereduari eramaten zaio.

12 irudia - seinale txikiko MOSFET eredua

KORRONTEA - 2. Metal-oxido FIC erdieroalea (MOSFET)

KORRONTEA - 2. Metal-oxido FIC erdieroalea (MOSFET) AURREKOA- EZAZU. FETen abantailak eta desabantailak

AURREKOA- EZAZU. FETen abantailak eta desabantailak