7. Ordenagailu Simulazioetarako FET ereduak

Ordenagailu Simulazioetarako FET ereduak

SPICE eta MICRO-CAPek JFET eta MOSFET modeloentzako modelo sofistikatuak dituzte. JFET eredua ( SPICE 2G.6 eredua) 12 parametroak ditu. MOSFET SPICE ereduak 42 parametroak ditu hiru mailatan. Gutxieneko mailako eredua 25 parametroak dauzka, baina goi mailako ereduak zerrendari gehituko zaizkio. MICRO-CAP 10 parametro osagarriak MOSFET ereduari 52-ra eramateko. Modeloak parametro gehiago erabiltzen ditu, simulazioaren emaitzak gailuaren funtzionamenduari hurbiltzea. Hala eta guztiz ere, zenbat eta parametro gehiago izan ereduan, azkarrago simulazioa exekutatzen da.

Hainbeste parametro egotearen arrazoia da modeloa gailuaren funtzionamendu-kurba ez-linealak gertutik imitatzen saiatzea dela. Ordenagailua eskuz guk baino askoz xehetasun gehiago jarraitzeko gai da, beraz, modeloa "paperezko" irtenbide baterako erabiltzen duguna baino sofistikatuagoa izan daiteke. Analisi egoera askotan, modeloaren parametro gehienak lehenetsitako balioetara ezarriko zenituzke eta eredu konplexu honek eztabaidatu ditugun eredu sinplifikatuen ia berdina jokatzen du. Eztabaidatzen dugun bitartean SPICE testu honen eranskinean, orain azkar aztertuko dugu sintaxia JFET edo MOSFET zirkuitu batean sartzeko. The SPICE JFET baterako adierazpena inprimakia da.

Jenda nd ng ns ereduaren izena [area] [OFF] [IC = vds [, vgs]]

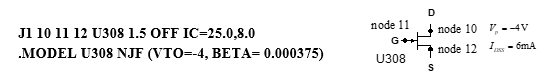

Parentesi karratuek adierazten dute kantitatea hautazkoa dela. Adibide gisa, baliteke adierazpenak sartzea,

Lehenengo adierazpeneko 10, 11 eta 12ak hustubidearen, atearen eta iturriaren nodo zenbakiak dira. U308 modeloaren izena da. Batasunak lehenetsitako eremuak ereduaren parametroak biderkatu edo banatzen ditu. "OFF" instrukzioak JFET itzaltzen du lehen eragiketa punturako. "IC" k hasierako baldintzak ezartzen ditu iturri-iturri eta atetik iturri tentsioetarako. Hasierako baldintzak analisi iragankorretarako bakarrik erabiltzen dira. Bigarren adierazpena U308 izena duen gailua gailu gisa definitzeko erabiltzen da n-kanal JFETrekin Vp (VTO) -4V eta K(BETA) berdina K = IDSS/VP2. batentzat p-canal JFETek PJF izendapena erabiltzen du NJFen ordez eta VTO eta BETA parametroak ezarri ditu p-kanalaren parametroak.

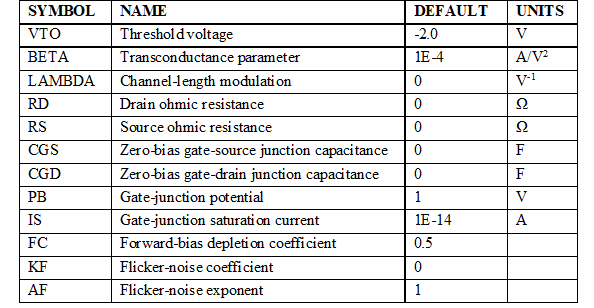

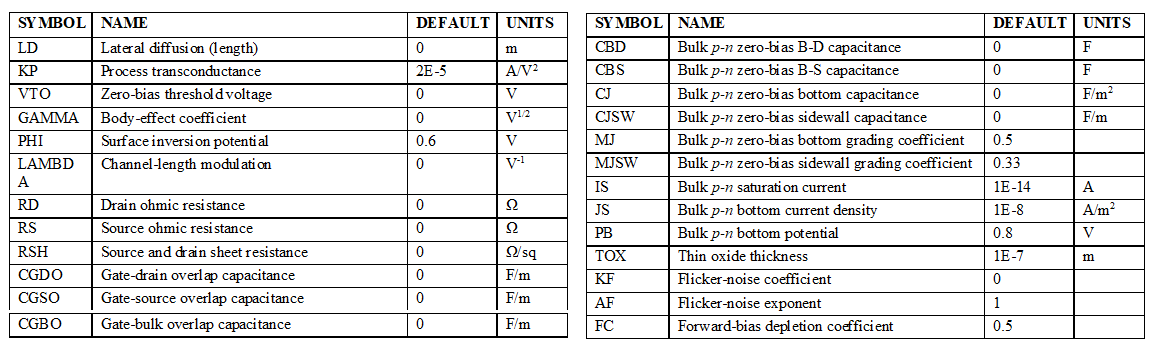

Hurrengo taulan ordenagailuen simulazio ereduan 12 parametroak zerrendatzen dira. Parametro bakoitzerako balio lehenetsia eta unitateak ere erakusten ditu.

2. taula - SPICE JFET parametroak

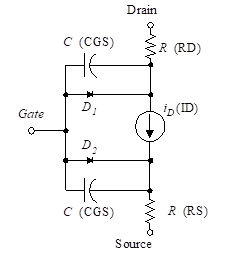

Parametro horiekin lotutako eredua 29 irudian erakusten da.

The SPICE MOSFET eredua JFETekoa baino askoz ere konplexuagoa da. Gutxieneko maila (Maila 1) 25 taulan zehaztutako 3 parametroak ditu. The SPICE adierazpena forma da:

Mname nd ng ns nb model name

+ [L = luzera] [W = zabalera] [AD = drainarea] [AS = sourcearea]

+ [PD = drainperiphery] [PD = sourceperiphery] [NRD = drainsquares]

+ [NRS = sourcesquares] [NRG = gatesquares] [NRB = bulksquares]

+ [OFF] [IC = vds] [, vgs [, VBS]]]

(29)

(29)

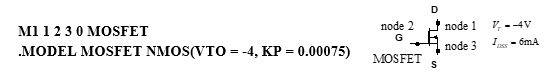

Parentesi karratuek adierazten dute kantitatea hautazkoa dela. Adibide gisa, adierazpen bat sar dezakezu,

Adibide honetan 1,2,3 eta 0 nodo zenbakiak zehazten dira gailuaren ihesa, atea, iturria eta gorputza. Kontuan izan KP = 2K (= 2IDSS/VP2). Erabili PMOS p-kanal ordez NMOS bigarren adierazpenean.

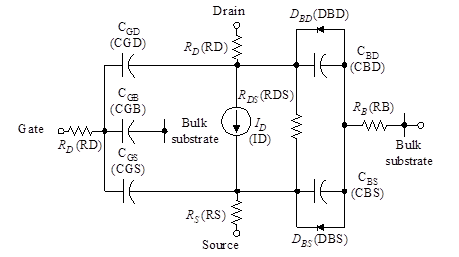

Parametroak, lehenetsitako balioak eta unitateak 3 taulan ematen dira. Parametro horiekin lotutako eredua 30 irudian erakusten da.

30 - MOSFET transistor eredua

GAUR EGUNGO - 7. FET ereduak ordenagailu bidezko simulazioetarako

GAUR EGUNGO - 7. FET ereduak ordenagailu bidezko simulazioetarako AURREKOA- EZAZU. MOSFETen konparazioa JFETrekin

AURREKOA- EZAZU. MOSFETen konparazioa JFETrekin