8. FET anplifikadoreak - Konfigurazio Canonikoak

FET anplifikadoreak - Konfigurazio Canonikoak

31 - FET anplifikadorea - konfigurazio orokorra

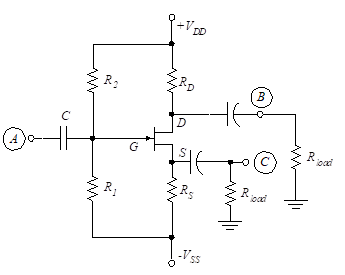

Figure 31-ek FET anplifikadorearen konfigurazio orokorra erakusten du.

Irudi honetan, sinbolo bat erakusten dugu n-channel JFET, baina konfigurazioa beste FET gailu batzuekin aplikatzen da iturrien ikurraren arabera. Irteera (karga) B edo C puntuan konektatuta dago eta sarrera C edo Arekin konektatuta dago.

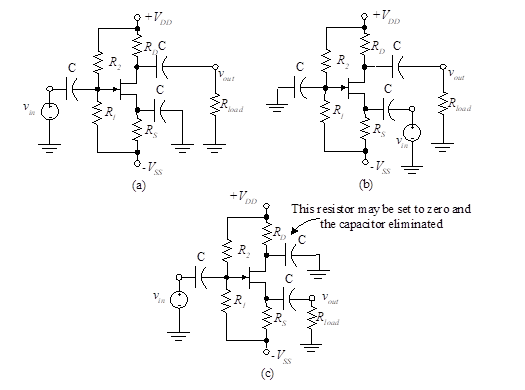

Fase bakarreko BJT anplifikadorearen lau oinarrizko konfigurazio egon ziren moduan, lau konfigurazio daude etapa bakarreko FET anplifikadorearentzat. Konfigurazio horiek 32 irudian erakusten dira.

32 irudian (a) irudian eman dugu ac JFET iturri terminaletik lurrera bidea. Irteera ihesa eta beheko aldea da, eta sarrera atea eta lurraren artean dago. JFET iturburu terminalak sarrera eta irteerarako ohikoa denez, hau deitzen da iturri arrunta (CS) anplifikadorea. 9.1 atalean ikusiko dugu konfigurazio honek sarrera erresistentzia handia eta goi-tentsioko errendimendua ematen duela, baina irteerako erresistentzia handiaren kaltetan.

JFET iturburu terminalaren eta beheko gaitasunaren artean 32 (a) irudian kentzen bada, hau daukagu iturburuko erresistentzia duen iturri arruntaren anplifikadorea (Edo iturburu-erresistentzia anplifikadorea). Hau igorle erresistentziarekin duen CE anplifikadorearen antzekoa da igorle-erresistentzia anplifikadorea).

32 irudian (b) irudian (dugu)ac) atearen terminalaren oinarriak, irteera drainatzetik lurrera eraman zuen eta JFET iturburu terminalaren arteko sarrera seinalea lurrean aplikatu zuen.

Atea (geroztik)ac) sarrera eta irteerako komuna, hau bezala ezagutzen da ate komuna (CG) anplifikadorea. 9.2 atalean ikusiko dugu konfigurazio honek tentsio handiko irabazia eta irteerako erresistentzia baxua ematen duela, baina sarrera baxuko erresistentziaren ondorioz. Sarrera baxuko erresistentziaren ondorioz, konfigurazio hori uneko anplifikadorea izaten da, unitateko uneko irabaziarekin (adibidez, seinaleak isolatzeko) hurbiltzen dena.

32 irudia - FET bakarreko etapa anplifikadorearen konfigurazioak

Azkenean, 32 irudia (c) drainatzea oinarri duen konfigurazioa erakusten duac), atea lurrean sartutako seinalea eta JFET iturburu terminaletik irteera lurrean. Ihesa oso ohikoa denez (ac) sarrera eta irteerarako, hau da ohiko ihesa (CDa) konfigurazioa. Bestela, deitzen zaio iturri jarraitzailea (SF) funtzionatzeko moduagatik. "9.3 CD (SF) anplifikadorea" atalean ikusiko dugu tentsio irabazia batasunetik gertu dagoela irteerako erresistentzia txikiarekin eta sarrerako erresistentzia handiarekin. Irteerak (JFET iturburuko terminalak) sarrera "jarraitzen" du eta konfigurazio hau buffer gisa erabili ohi da.

GAUR EGUNGO - 8. FET anplifikadoreak - Konfigurazio kanonikoak

GAUR EGUNGO - 8. FET anplifikadoreak - Konfigurazio kanonikoak AURREKOA- EZAZU. Ordenagailu Simulazioetarako FET ereduak

AURREKOA- EZAZU. Ordenagailu Simulazioetarako FET ereduak