4. FET anplifikadorearen konfigurazioak eta alborapena

FET anplifikadorearen konfigurazioak eta alborapena

BJTen biasa egiteko erabiltzen diren planteamenduak MOSFETS alboratzeko ere erabil daitezke. Ikuspegiak osagai diskretuen anplifikadoreak zirkuitu integratuaren anplifikadoreetarako erabil daitezke. Osagai diskretuen diseinuak akoplamendu handiak eta saiheskailu alternatiboak erabiltzen dituzte anplifikadorearen etapa bakoitzeko DC polarizazioa isolatzeko, osagai diskretuen BJT anplifikadoreak bezala. IC MOSFET anplifikadoreak, oro har, zuzeneko akoplamenduak dira, kondentsadoreak handiak ez direlako. IC MOSFET anplifikadoreek BJT IC anplifikadoreak erabiltzen dituzten antzeko korronteen iturriak erabiltzen dituzte.

4.1 osagai diskretuen MOSFETren alborapena

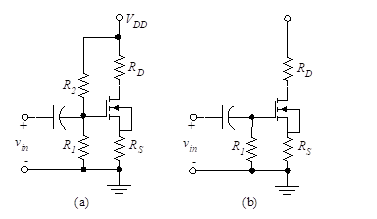

MOSFET anplifikadoreen osagai diskretuen bereizketa 21 irudian agertzen diren zirkuituekin lortzen da. Atea-to-iturriaren tentsioak transistore horren konfigurazioan beharrezkoa den zirkuitu mota zehazten du. Hobekuntza moduko transistore baterako, beti izango da beharrezkoa tentsio positiboa atean. Tentsio banaketa alborapenean, izango da R1 R2 tentsio positiboa lortzeko. MOSFET edo JFET agortzeagatik, R2 bukaera edo infinitua izan daiteke, 21 irudian (b) irudian erakusten den moduan.

21. irudia - Anplifikadorearen alborapen konfigurazioak

Ohiko iturria (CS)- the ac sarrera aplikatzen da CGeta, ac irteera hartu da CD, eta CS da dc tentsio iturria edo lurra. Hau BJTren igorle arrunten konfigurazioaren antzekoa da.

-Iturriaren erresistentzia (SR) - the ac sarrera aplikatzen da CGeta, ac irteera hartu da CD CS ezean. Hau BJTren igorle-erresistentziaren konfigurazioaren antzekoa da.

-Atari arrunta (CG) - the ac sarrera aplikatzen da CSeta, ac irteera hartu da CD CG da dc tentsio iturria edo lurra. Batzuetan CG konfigurazioan, CG ezean eta atea zuzenean konektatuta dago dc tentsio hornidura. CGa BJTren oinarrizko konfigurazio komuna antzekoa da, nahiz eta oso gutxitan ikusten diren zirkuituetan.

-Iturriaren jarraitzailea (SF) - the ac sarrera aplikatzen da CGeta, ac irteera hartu da CS eta ihesa bat dago konektatuta dc zuzenean edo bidezko tentsio hornidura CD. Hau batzuetan ihesa arrunta deitzen zaio (CD) eta BJTren igorle jarraitzailearen konfigurazioaren antzekoa da.

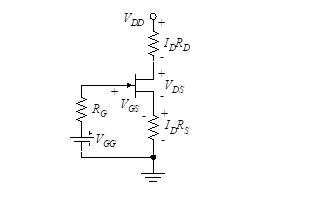

22 irudia - Thevenin zirkuitu baliokidea

Konfigurazio horietako bakoitza xehetasun gehiagorekin aztertzen da 9. atalean, "FET anplifikadorearen analisia".

Konfigurazio ezberdinak kondentsadoreen bidezko konexioetan aldatzen direnez, eta kondentsadoreak zirkuitu irekiak dira dc tentsioak eta korronteak, azter ditzakegu dc kasu orokorreko alborapena. Anplifikadoreen diseinurako, transistorea funtzionamendu aktiboaren eskualdean funtzionatu nahi dugu (saturazio eskualdea edo apurtzeko modua ere identifikatzen dena), beraz, gailuaren IV. Ezaugarri bat hartzen dugu. (Beti egiaztapen hau egiaztatu beharko genuke diseinuaren amaieran!)

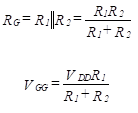

Biasa analisia errazteko, Thevenin iturri bat erabiltzen dugu transistorearen atean zirkuituaren eredua 22 irudian erakusten den moduan.

(24)

Bi aldagai ezezagun daudenez gero, alborapena ezartzekoID, VGS, eta VDS), hiru behar ditugu dc ekuazioak. Lehenik eta behin, dc ate-iturriaren begiaren inguruko ekuazioa idazten da.

![]()

(25)

Kontuan izan atea unekoa zero denez, zero tentsio jaitsiera existitzen dela RG. Bigarrena dc ekuazioa Kirchhoff-en legearen ekuaziotik aurkitzen da drainatze-iturri begizta.

![]()

(26)

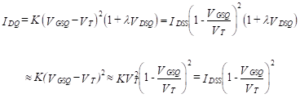

Hirugarren dc biasa puntua zehazteko beharrezko ekuazioa Ekuazioan (20) aurkitu da  atalean ”Junction field-effect transistor (JFET)" Hemen errepikatzen dena.

atalean ”Junction field-effect transistor (JFET)" Hemen errepikatzen dena.

(27)

Lehenengo hurbilketa aplikatuko da |λVDS| << 1 (ia beti egia da) eta parekatutako ekuazioen ebazpena nabarmen sinplifikatzen du.

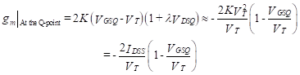

Ekuazioa jarri dezakegu gm [Ekuazioa (22)]

(22)

diseinuan erabilgarria izango den antzeko formatu batean sartu.

(28)

Ekuazioak (25) - (28) nahikoa dira alborapena zehazteko. MOSFET anplifikadore diskretuen kasuan, ez dugu Q-puntua jarri beharrik ac kargatu lerroa maiz BJT-ren alborapenean egin dugun bezala. Hori dela eta, FETko anplifikadore diskretuak normalean anplifikadorearen kate baten lehen etapa gisa erabiltzen dira sarrera erresistentzia handia aprobetxatzeko. Lehenengo fasean edo preamplifier, tentsio mailak hain txikiak dira eta ez dugu preamplifikadorearen irteera txango handietan gidatzen.

GAUR EGUNGO - 4. FET anplifikadorearen konfigurazioak eta alborapena

GAUR EGUNGO - 4. FET anplifikadorearen konfigurazioak eta alborapena AURREKOA- EZAZU. Lotura eremuko efektu-transistorea (JFET)

AURREKOA- EZAZU. Lotura eremuko efektu-transistorea (JFET)