SystemC SIMULATION

SystemC SIMULATION

- Verilog-A & AMS-simulaatio

- SystemVerilog-simulaatio

- Verilog Simulation

- VHDL-simulointi

- VHDL-AMS-simulaatio

SystemC on toinen suuri työkalu laitteiston mallintamiseen. Se sisältää kaikki C ++: n ominaisuudet, joita käytetään kaikkialla maailmassa, ja C ++ -luokan kirjasto, joka on erityisesti suunniteltu järjestelmän suunnitteluun. SystemC: llä on avoimen lähdekoodin vapaa toteutus ja voit kääntää sen erittäin tehokkaaksi suoritettavaksi binäärikoodiksi, jossa on myös ilmainen Visual Studio Community C ++ -kääntäjä. SystemC-järjestelmässä laitteistoa voidaan mallintaa korkeammalla abstraktiotasolla kuin muissa HDL-laitteissa ja niinpä hyvin monimutkaisten laitteiden, kuten mikrokontrollerien, mallinnuksessa on helpompaa ja tehokkaampaa käyttää kuin muut HDL: t, kuten VHDL tai Verilog.

V11issa ja myöhemmissä TINA-versioissa voit myös luoda ja käyttää järjestelmässä mallinnettuja komponentteja sekä TINA: ssa että TINACloudissa. Seuraavat ovat vaatimukset, jotka koskevat SystemC: n käyttöä TINA: lla.

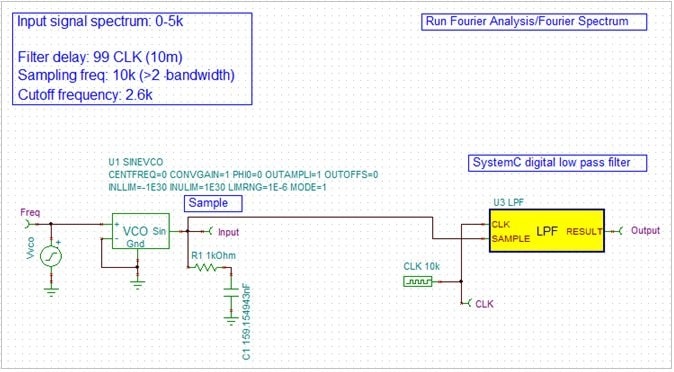

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

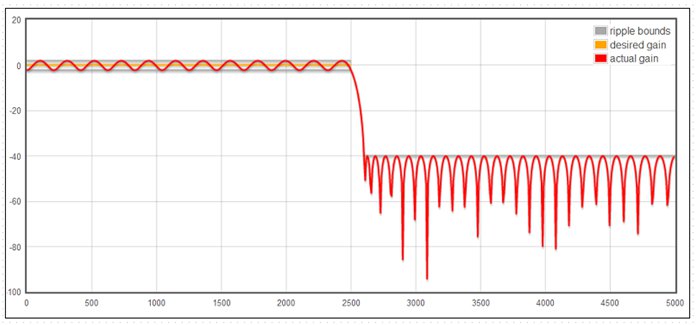

Suodattimen ominaisuudet ja C-koodi on suunniteltu vapaalla työkalulla osoitteessa

http://t-filter.engineerjs.com/

Luotu C-koodi sijoitettiin fir.cpp-tiedostoon.

Suorita analyysi / Fourier-analyysi / Fourier-spektri…

paina

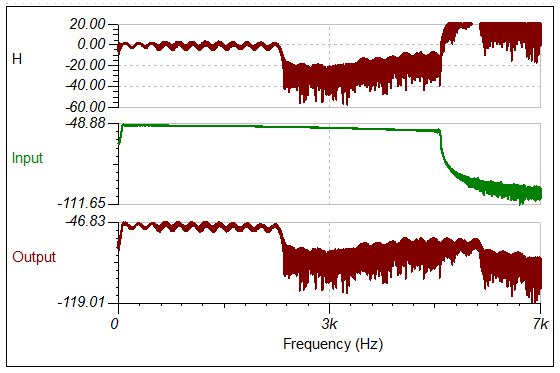

paina Lisää: painiketta. Tyyppi Ulostulo (t) / tulo (s) rivin muokkauksessa. Kirjoita uuteen funktion nimeen H. Lehdistö luoda. lehdistö OK. Valita Näytä / erilliset käyrät.

Tuloksena on seuraava

SystemC-makron tärkein osa:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.