1 差動アンプ

差動アンプ

ほとんどのオペアンプは、1つのチップ上に完全なシステムを形成する一連のトランジスタ、抵抗、およびコンデンサで構成されています。 現在入手可能なアンプは、信頼性が高く、サイズが小さく、消費電力が非常に少ないです。

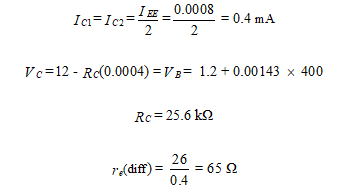

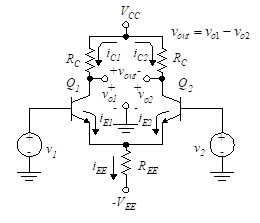

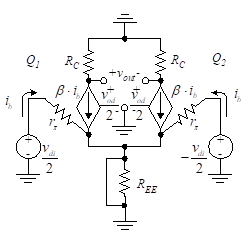

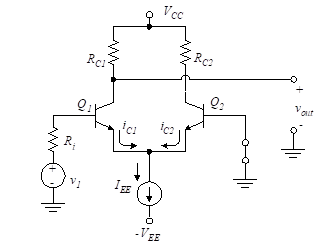

ほとんどのオペアンプの入力段はDです。差動アンプ 図1の最も単純な形式で示されているように。

図1 - 差動アンプ

差動アンプは2つのエミッタ結合コモンエミッタで構成されています dc アンプ。 2つの入力があります、 v1 & v2、そして3つの出力、 vo1, vo2 & vでる。 3番目の出力 vでるは、の違いです vo1 & vo2.

1.1のDC伝達特性

差動アンプは、大信号入力ではリニアに動作しません。 分析を簡単にするために、REが大きい、各トランジスタのベース抵抗が無視できること、そして各トランジスタの出力抵抗が大きいと仮定する。 ここで使用されている抵抗は大きく、電流源の等価抵抗である可能性があるため、差動アンプではREではなくREEを使用しています。 REEの値が大きいと、エミッタ抵抗の電圧降下はほぼ一定に保たれます。

この回路で出力電圧を求めます。 図1の回路のベース接合ループの周りにKVL方程式を書くことから始めます。

(1)

(2)

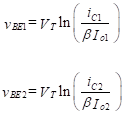

コレクタ電流の式を見つける必要があります。 iC1 & iC2。 ベース - エミッタ間電圧は次式で与えられます。

式中(2) Io1 & Io2 の逆飽和電流は Q1 & Q2 それぞれ。 トランジスタは同一であると仮定される。 式(1)と(2)を組み合わせると、

(3)

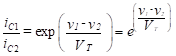

電流比について式(3)を解くと、

(4)

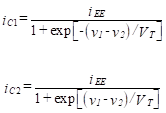

想定できます iC1 にほぼ等しい iE1 & iC2 にほぼ等しい iE2。 したがって、

(5)

式(4)と(5)を組み合わせると、

(6)

注意してください

(7)

式(6)を見ると重要な観察ができます。 もし v1 – v2 数百ミリボルトより大きくなると、トランジスタXNUMXのコレクタ電流は小さくなり、トランジスタは本質的に遮断される。 トランジスタXNUMXのコレクタ電流は、にほぼ等しい。 iEEこのトランジスタは飽和している。 コレクタ電流、したがって出力電圧 vでる、2つの入力電圧の差とは無関係になります。

線形増幅は約100 mV未満の入力電圧差に対してのみ発生します。 入力電圧の直線範囲を広げるために、小さなエミッタ抵抗を追加することができます。

1.2コモンモードゲインとディファレンシャルモードゲイン

差動アンプは、2つの入力電圧の差にだけ応答するように設計されています。 v1 & v2。 しかし、実際のオペアンプでは、出力はある程度これらの入力の合計に依存します。 例えば、両方の入力が等しい場合、出力電圧は理想的にはゼロであるべきですが、実際のアンプではそうではありません。 回路がその差に応答した場合を、 差動モード。 2つの入力を等しくすると、回路は コモンモード。 理想的には、回路が差動モードでのみ出力を生成することを期待します。

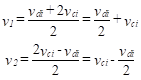

任意の2つの入力電圧 v1 & v2は、共通部分と差動部分に分解できます。 以下の2つの新しい入力電圧を定義します。

(8)

電圧、 vdiは差動モード入力電圧であり、単純に2つの入力電圧の差です。 電圧、 vciは同相入力電圧であり、2つの入力電圧の平均です。 元の入力電圧は、次のようにこれらの新しい量で表すことができます。

(9)

2つの入力電圧を等しく設定すると、

(10)

2つの入力が等しいので、エミッタ - ベース接合電圧は等しい(トランジスタが同一の場合)。 従って、コレクタ電流もまた同一でなければならない。

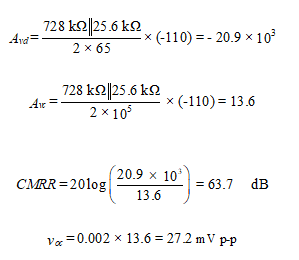

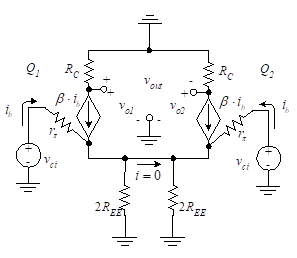

図2(a)差動モードアンプ等価回路

図2(a)に示すように、差動モード入力電圧の等価回路を見ます。 の電流として Q1 回路が増加すると、 Q2 回路は同じ速度と振幅で減少します。 これは、 Q2 と等しい Q1 しかし180o 位相がずれています。 したがって、両端の電圧変化は REE ゼロです。 以来 ac 両端の信号電圧 REE ゼロである、それはの短絡によって取り替えることができます ac 等価回路。 振幅が等しいが180である各トランジスタのベースに電圧をかけることに注意すること。o 位相がずれているということは、2つのトランジスタのベース間に2倍の振幅の電圧を印加することと同じです。 での電圧 vo1 & vo2 振幅は等しいが位相が反対で、差動モード利得は

(11)

この差動モード利得は、 シングルエンド出力 それは1つのコレクターと地面の間で取られるので。 出力が間に取られる場合 vo1 & vo2差動モード利得は、 両端出力 そしてによって与えられる

(12)

同様の解析を図2(b)の同相等価回路にも適用できます。

図2(b)コモンモードアンプ等価回路

抵抗器を分割すれば REE それぞれ元の抵抗の2倍の2つの並列抵抗に変換すると、回路の半分だけを分析することによって出力を見つけることができます。 トランジスタは同一で、コモンモード入力電圧は等しく同相であるため、2の両端の電圧はREE 抵抗器は同じです。 したがって、で示されている2つの並列抵抗間の電流はゼロで、回路の片側だけを見ればいいのです。 コモンモード電圧利得は、

(13)

式(13)は、 REE 大きくて re<<REE.

以下のように、コモンモードおよび差動モード利得の観点からダブルエンド出力電圧を求めます。

(14)

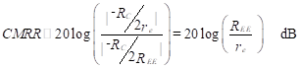

アンプが主に入力電圧間の差に反応するように、差動モード利得が同相モード利得よりはるかに大きいことが望ましい。 の コモンモード除去比、CMRRは、同相モード利得に対する差動モード利得の比として定義されます。 通常はdBで表されます。

(15)

差動モードと同相モードの両方でアンプの入力抵抗を決定します。 差動モードでは、両方のトランジスタのベースにあるアンプを調べます。 これにより、両方のトランジスタのエミッタを通る完全な回路が得られ、入力抵抗は

(16)

コモンモード入力については、図2(b)のアンプを見てください。 したがって、入力抵抗は

(17)

これらの結果は、コモンモードの入力抵抗が差動モードの入力抵抗よりはるかに高いことを示しています。

当社の差動アンプ解析は、トランジスタ構成要素としてのBJTに基づいています。 FETは差動アンプにも使用でき、その結果、入力バイアス電流が減少し、入力インピーダンスがほぼ無限大になります。 FETを用いた差動増幅器の解析は、BJT解析と同様にして行われる。

差動増幅器は回路が正しく動作することを保証するために整合トランジスタを必要とする。 差動増幅器が集積回路上にある場合、2つのトランジスタが同じ材料を用いて同時に製造されるので、この追加の要求はそれほど問題ではない。

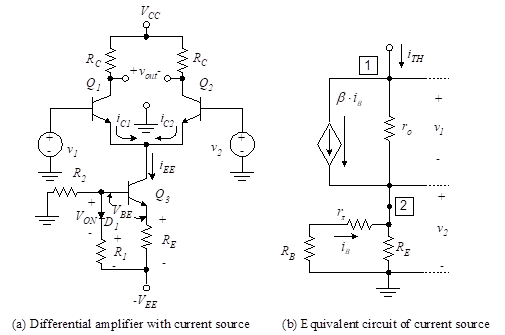

定電流源付き1.3差動アンプ

作ることが望ましい REE コモンモード出力を減らすために、できるだけ大きくします。 式は、CMRRを大きくするためには次のようにしなければならないことを示しています REE 大。 大きな抵抗をICチップ上に製造することは困難であるので、我々は別の方法を模索する。 これは交換することによって達成されます REE また、 dc 現在のソース。 理想的な電流源は無限のインピーダンスを持っているので、交換の可能性を調査します。 REE そのような電流源で。 図9.3は、抵抗が REE、は定電流源に置き換えられます。

(18)

信号源が理想的な定電流源に近ければ近いほど、同相除去比は高くなります。 ダイオード補償の固定バイアス電流源について説明します。 補償により、回路の動作が温度変動に左右されにくくなります。 ダイオード D1 とトランジスタ Q3 これらは、動作温度範囲にわたってほぼ同じ特性を持つように選択されています。

図3(a)の回路を解析してCMRRを求めるには、等価抵抗を求める必要があります。 RTH (定電流源回路のテブナン相当)。 等価抵抗は次の式で与えられます[図3(b)を参照]。

ノード1でKCL方程式を書くと、

(19)

コラボレー ro 指定された動作点におけるトランジスタの内部抵抗です。 それはによって与えられる

(20)

図3 - 定電流源付き差動アンプ

ノード2でのKCL方程式は次のようになります。

(21)

コラボレー

(22)

代入 v1 & v2 ノード2で方程式に入ると、

(23)

最後に、テブナン抵抗は、式(22)と(23)を式(18)に代入することによって与えられます。

(24)

この表現を非常に単純化するために一連の仮定をします。 バイアスの安定性を維持するために、次のガイドラインを使用します。

(25)

この値を代入する RB 式(24)に β、 我々は持っています

(26)

この表現を簡単にすることができます

(27)

それから

(28)

この方程式の2番目の項は最初の項よりはるかに大きいので、無視できます。 RE 入手

(29)

次の条件が存在する場合、この方程式はさらに単純化できます。

(30)

その場合、単純な結果が得られます。

(31)

したがって、すべての近似が有効であれば、 RTH から独立している β そしてその価値は非常に大きいです。

シングルエンド入出力付き1.4差動アンプ

図4は、2番目の入力が v2はゼロに設定され、出力は次のようになります。 vo1.

代わりに定電流源を使用します。 REE前のセクションで説明したように、 これは 位相反転付きシングルエンド入力および出力アンプ。 アンプは設定によって分析されます v2 上記の式では= 0です。 差動入力は

(32)

だから出力は

(33)

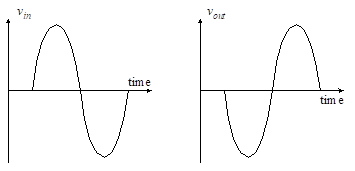

図4 - 位相反転を伴うシングルエンド入力

マイナス記号はこのアンプが180を示すことを示しますo 出力と入力間の位相シフト 典型的な正弦波入力と出力を図5に示します。

図5 - 正弦波入力および出力

出力信号がグランドを基準としているが、位相反転が望ましくない場合は、出力をトランジスタから取得することができます。 Q2.

例1-差動増幅器(分析)

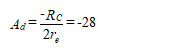

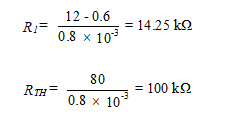

図1に示す回路の差動電圧利得、同相電圧利得、およびCMRRを求めます。 と仮定する Ri = 0、 RC = 5kΩ、 VEE = 15 V、 VBE = 0.7 V、 VT = 26 mV REE = 25kΩ。 みましょう v2 = 0から出力を取得します。 vo2.

解決法: 流れる電流 REE 静止状態で見つかります。 のベース以来 Q2 が接地されていると、エミッタ電圧は VBE = 0.7 V、および

各トランジスタの静止電流はこの量の半分です。

Since

各トランジスタの差動電圧利得は

同相モード電圧利得は

同相モード除去比は次式で与えられます。

お申込み

また、TINAまたはTINACクラウドサーキットシミュレータを使用して、下のリンクをクリックしてインタープリタツールを使用してこれらの計算を実行することもできます。

例

例1に記載されている差動アンプの場合は、次のように温度補償された固定バイアス電流源(図3)を設計します。 REE そして、差動アンプの新しいCMRRを ro = 105kΩ、 VBE = 0.7 V、および β = 100 仮定する R1 = R2.

解決法: トランジスタの動作点を中央に配置します。 dc 負荷線

次に、図3(a)の電流源を参照して

バイアス安定性のために、

その後

創立0.1年RE>>re (つまり、1.25kΩ>> 26/0.57Ω)、式(31)から次のようになります。

CMRRは

お申込み

また、TINAまたはTINACクラウドサーキットシミュレータを使用して、下のリンクをクリックしてインタープリタツールを使用してこれらの計算を実行することもできます。

例

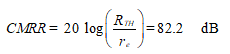

最大出力電圧振幅が図6に指定されている条件を満たすように回路を設計します。 5つのトランジスタ Q1 〜へ Q5、それぞれ持っている β = 100 Q6 ています β 200の。 VBE すべてのトランジスタの0.6 V VT = 26 mV VA すべてのトランジスタが同一であると仮定する。

決定する、

(a) RC, R1、およびCMRR。

(b)コモンモード出力電圧。

(c)差動モード出力電圧。

(d)差動モード 電圧 vdi 最大出力用です。

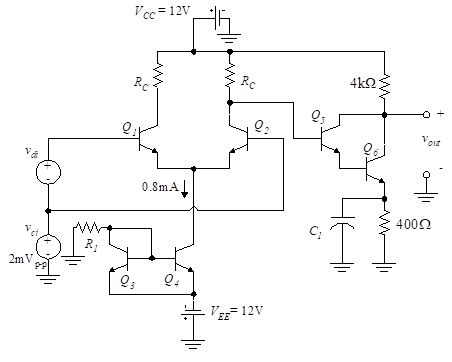

解決法: 回路を3つのセクションで扱います。

- 1 ダーリントンアンプ。

- 2 差動アンプ

- 3 単純な電流源

システム全体については、

差動入力 vdi 歪みのない最大出力電圧振幅を得るのに必要な

また、TINAまたはTINACクラウドサーキットシミュレータを使用して、下のリンクをクリックしてインタープリタツールを使用してこれらの計算を実行することもできます。

電流–1。差動アンプ

電流–1。差動アンプ 前のページ - 実用オペアンプ - はじめに

前のページ - 実用オペアンプ - はじめに