2. Shifters Tahap

Shifters Tahap

Walaupun input kepada penguat mempunyai nilai purata voltan sifar, output biasanya mempunyai voltan bukan sifar purata disebabkan oleh kesan biasing. Ini dc voltan boleh menyebabkan kerugian yang tidak diingini yang menjejaskan operasi sistem.

Sejak op-amp adalah multi-stage dc penguat dengan keuntungan tinggi, tidak diingini dc voltan boleh menjadi punca kebimbangan. Satu offset kecil di peringkat awal dapat menembus peringkat kemudian.

Peralihan tahap adalah penguat yang menambah atau menolak voltan yang diketahui dari input untuk mengimbangi dc voltan mengimbangi. Op-amp mempunyai peralihan peringkat termasuk dalam reka bentuk mereka.

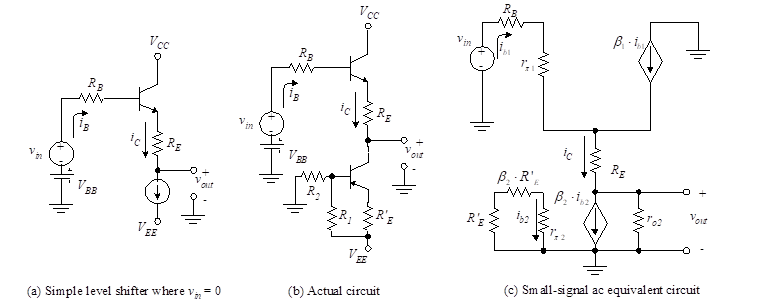

Rajah 7 menggambarkan kedudukan mudah. Kami menunjukkan bahawa shifter ini bertindak sebagai penguat unit-gain untuk ac sambil menyediakan laras dc output.

Kami memulakan analisis dengan menggunakan KVL dalam gelung input Rajah 7 (a) dan membiarkan vin = 0 untuk mendapatkan

(34)

Sejak sekarang

(35)

kita selesaikan dc nilai voltan keluaran, Vkeluar.

(36)

Persamaan (36) menunjukkan bahawa dengan mengubah RE, Vkeluar boleh ditetapkan ke mana-mana yang dikehendaki dc tahap (terhad kepada maksimum VBB-VBE). Sejak VBB adalah dc tahap diperolehi dari peringkat terdahulu, penguat ini digunakan untuk mengalihkan tahap ke bawah (kepada nilai yang lebih rendah). Jika menaik peralihan diperlukan, litar serupa digunakan tetapi pnp transistor digantikan untuk npn transistor. Litar lengkap dengan sumber arus aktif ditunjukkan dalam Rajah 7 (b).

Rajah 7- Tahap shifter

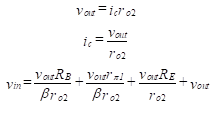

Kami kini memeriksa litar dengan ac isyarat digunakan. Rajah 7 (c) menggambarkan ac litar bersamaan. Perhatikan bahawa β2ib2 adalah arus pemungut dalam sumber arus aktif, dan kami mengandaikan ia menjadi tetap. Kerana ia ac nilai semasa adalah sifar, sumber semasa ini digantikan oleh litar terbuka. Kami menulis ac persamaan menggunakan KVL.

(37)

and

(38)

Nisbah ac output kepada ac input adalah

(39)

Persamaan (39) menunjukkan bahawa sebagai ro2 menjadi besar, nisbah output untuk input pendekatan perpaduan dan tahap shifter bertindak seperti pengikut pemancar untuk ac. Inilah hasil yang dikehendaki.

Contoh

Dua penguat CE yang digabungkan langsung diletakkan dalam siri untuk mencapai keuntungan voltan yang dikehendaki. Reka bentuk shifter tahap yang akan ditempatkan di antara dua penguat CE untuk menyediakan a dc voltan yang cukup rendah untuk mencegah penguat CE kedua dari tepu. Lakukan ini dengan memberikan kecenderungan 1 V ke peringkat kedua. Pengumpul voltan, VC, penguat pertama adalah 4 V, dan RC penguat itu adalah 1 kΩ. Reka bentuk tahap shifter untuk mempunyai IC daripada 1 mA menggunakan a ![]() bekalan kuasa. Gunakan sumber arus jenis yang ditunjukkan dalam Rajah 3 (Lihat bab: Penguat ubah 1.3) dengan transistor yang mempunyai β (s) = 100, VBE(S) = 0.7 V, dan VON = 0.7 V.

bekalan kuasa. Gunakan sumber arus jenis yang ditunjukkan dalam Rajah 3 (Lihat bab: Penguat ubah 1.3) dengan transistor yang mempunyai β (s) = 100, VBE(S) = 0.7 V, dan VON = 0.7 V.

penyelesaian: Shifter tahap ditunjukkan dalam Rajah 7 (b). Kita perlu mencari nilai-nilai RE, R1, R2, dan R 'E. Sejak penguat pertama mempunyai VC daripada 4 V, nilai VBB untuk Persamaan (36) adalah 4 V, sedangkan yang RB daripada formula itu ialah 1 kΩ. Perhatikan ini menggunakan litar setara Thevenin penguat sebelumnya. Persamaan (36) kemudian menghasilkan,

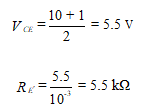

Menetapkan titik operasi transistor sumber semasa di tengah-tengah dc talian beban, kita ada

and

Voltan merentasi R 'E adalah 5.5 V. Kemudian

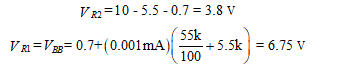

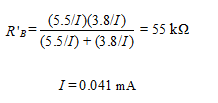

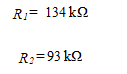

Kita sekarang tahu voltan merentasi R1 and R2 dan rintangan selari. Ini menghasilkan dua persamaan, di mana kita mengandaikan arus pangkalan di transistor bawah Rajah 9.7 (b) diabaikan.

and

Oleh itu, reka bentuk itu lengkap.

PERMOHONAN

Juga, anda boleh menjalankan pengiraan ini dengan simulator litar TINA atau TINACloud, menggunakan alat Interpreter mereka dengan mengklik pautan di bawah.

SEMASA - 2. Pengubah Tahap

SEMASA - 2. Pengubah Tahap PREVIOUS- 1. Penguat berbeza

PREVIOUS- 1. Penguat berbeza