2. FET semikonduktor logam-oksida (MOSFET)

FET semikonduktor logam-oksida (MOSFET)

FET semikonduktor logam-oksida (MOSFET) adalah empat peranti terminal. Terminal adalah sumber (S), pintu gerbang (G) and longkang (D). Yang substrat or badan membentuk terminal keempat. MOSFET dibina dengan terminal gerbang bertebat dari saluran dengan dielektrik silikon dioksida. MOSFET boleh sama ada kekurangan or mod peningkatan. Kami mentakrifkan kedua-dua istilah ini tidak lama lagi.

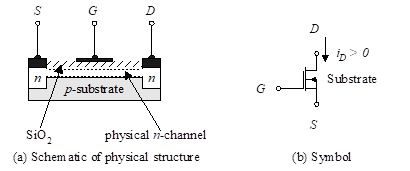

Rajah 1 - MOSFET pengurangan saluran-n

MOSFET kadang-kadang dirujuk sebagai IGFETs (Transistor Gate-Effect Gate) kerana SiO2 lapisan digunakan sebagai penebat antara pintu dan substrat. Kami memulakan analisis kami dengan mod MOSFET kekurangan. Sama seperti BJTs boleh sama ada npn or pnp, MOSFET boleh sama ada n-channel (NMOS) atau p-channel (PMOS). Rajah 1 menggambarkan struktur fizikal dan simbol untuk a n- MOSFET kekurangan saluran. Perhatikan bahawa substrat disambungkan ke terminal sumber. Ini akan selalu berlaku.

MOSFET habis dibina dengan a fizikal saluran yang dimasukkan di antara longkang dan sumbernya. Akibatnya, apabila voltan, vDS, digunakan antara longkang dan sumber, semasa, iD, wujud antara longkang dan sumber walaupun terminal gerbang G masih tidak berkaitan (vGS = 0 V).

Pembinaan bangunan n- MOSFET pengurangan saluran bermula dengan p-doped silikon. The n-doped sumber dan longkang saliran membentuk hubungan rintangan rendah antara hujung n- saluran, seperti yang ditunjukkan dalam Rajah 1. Lapisan silikon dioksida nipis diendapkan meliputi kawasan antara sumber dan longkang. The SiO2 adalah penebat. Lapisan aluminium didepositkan pada penebat silikon dioksida untuk membentuk terminal gerbang. Beroperasi, negatif vGS menolak elektron keluar dari kawasan saluran, dengan itu mengurangkan saluran. Bila vGS mencapai voltan tertentu, VT, saluran itu terputus. Nilai positif bagi vGS meningkatkan saiz saluran, mengakibatkan peningkatan arus saliran. Pengurangan MOSFET boleh beroperasi dengan nilai positif atau negatif vGS. Oleh kerana pintu itu terisolasi dari saluran, arus gerbang adalah kecil sekali (atas perintah 10-12 A).

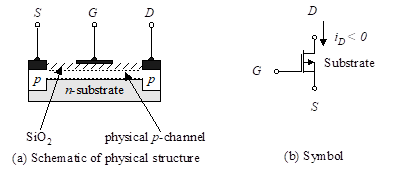

Rajah 2 - MOSFET pengurangan saluran-saluran

Rajah 2 adalah setanding dengan Rajah 1, kecuali bahawa kita telah menukar n- MOSFET pengurangan saluran kepada a p- MOSFET kekurangan saluran.

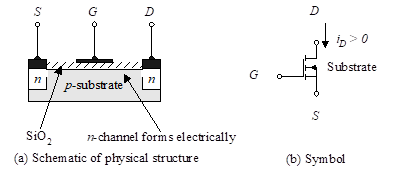

. n-Malaysian peningkatan MOSFET digambarkan dalam Rajah 3 bersama-sama dengan simbol litar. Ini adalah bentuk transistor kesan medan yang paling biasa digunakan.

Gambar MOSFET peningkatan 3 - n-saluran

. n-Malaysian peningkatan MOSFET berbeza daripada MOSFET yang hancur kerana tidak mempunyai nipis n-layer. Ia memerlukan voltan positif di antara pintu dan sumber untuk menubuhkan saluran. Saluran ini dibentuk oleh tindakan tegangan gate-to-source yang positif, vGS, yang menarik elektron dari rantau substrat antara n-didalam saluran dan sumbernya. Positif vGS menyebabkan elektron terkumpul di permukaan di bawah lapisan oksida. Apabila voltan mencapai ambang, VT, bilangan elektron yang mencukupi tertarik kepada rantau ini untuk membuatnya bertindak seperti menjalankan n- saluran. Tiada saliran semasa, iD wujud sehingga vGS melebihi VT.

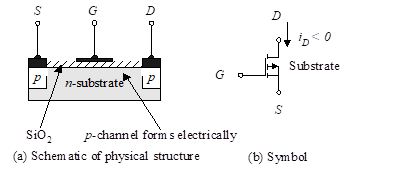

Rajah 4 adalah setanding dengan Rajah 3, kecuali bahawa kita telah menukar n- MOSFET peningkatan saluran ke a p-MOSFET peningkatan saluran.

Rajah 4 - MOSFET tambahan p-saluran

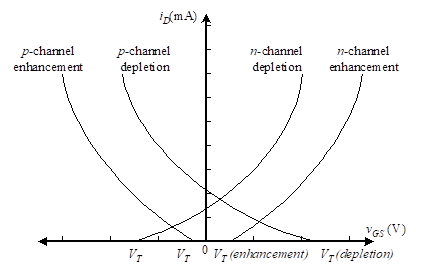

Sebagai ringkasan, keluarga MOSFET mempamerkan pengenalpastian iD berbanding vGS lengkung yang ditunjukkan dalam Rajah 5. Setiap lengkung ciri dikembangkan dengan voltan longkang-sumber yang mencukupi vDS untuk mengekalkan peranti di rantau operasi normal iD berbanding vDS lengkung. Perbincangan di bahagian kemudian akan menentukan voltan ambang VT untuk kedua-dua peningkatan MOSFET dan MOSFET pengurangan.

Gambar 5 - iD berbanding vGS ciri-ciri keluarga MOSFET untuk voltan sumber longkang yang mencukupi VDS

Ciri-ciri Terminal MOSFET Peningkatan 2.1

Sekarang setelah kami memaparkan struktur dan dasar dasar untuk operasi MOSFET, kami menggunakan pendekatan untuk memeriksa perilaku terminal dari perangkat mod peningkatan. Mari pertama kita membuat beberapa pemerhatian umum dari Gambar 1. Fikirkan aliran arus normal di MOSFET sebagai dari saluran pembuangan ke sumber (sama seperti di BJT, ia adalah antara pemungut dan pemancar). Seperti dengan npn BJT, dua diod back-to-back wujud di antara longkang dan sumber. Oleh itu, kita mesti menggunakan tegasan luaran ke pintu gerbang untuk membolehkan arus mengalir di antara longkang dan sumber.

Sekiranya kita mengalirkan sumbernya, dan menggunakan voltan positif ke pintu gerbang, voltan itu adalah voltan pintu-ke-sumber yang berkesan. Voltan pintu positif menarik elektron dan menangkis lubang. Apabila voltan melebihi ambang (VT), elektron yang cukup tertarik untuk membentuk saluran antara saluran dan sumber. Pada ketika ini, transistor menghidupkan dan arus adalah fungsi kedua-duanya vGS and vDS. Ia harus jelas VT adalah nombor positif untuk nperanti saluran, dan nombor negatif untuk a p-halaman saluran.

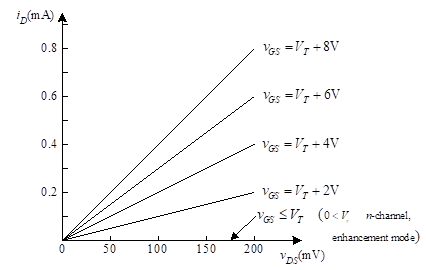

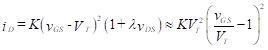

Sebaik sahaja saluran dibuat (iaitu, vGS >VT), aliran semasa boleh berlaku dalam saluran antara longkang dan sumber. Aliran semasa ini bergantung kepada vDS, tetapi ia juga bergantung kepada vGS. Apabila vGS hanya hampir tidak melebihi voltan ambang, arus yang sangat sedikit dapat mengalir. Sebagai vGS meningkat melebihi ambang, saluran itu mengandungi lebih banyak pembawa dan arus yang lebih tinggi adalah mungkin. Rajah 6 menunjukkan hubungan antara iD and vDS di mana vGS adalah parameter. Perhatikan bahawa untuk vGS kurang daripada ambang, tiada aliran semasa. Untuk yang lebih tinggi vGS, hubungan antara iD and vDS adalah kira-kira linear yang menunjukkan bahawa MOSFET berkelakuan seperti perintang yang rintangan bergantung kepada vGS.

Rajah 6 -iD berbanding vDS untuk mod peningkatan n-MOSFET saluran ketika vDS adalah kecil

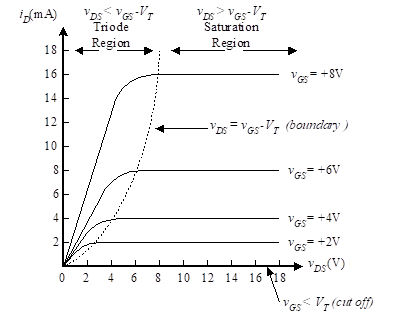

Keluk Rajah 6 kelihatan seperti garis lurus. Walau bagaimanapun, mereka tidak akan terus sebagai garis lurus ketika vDS semakin besar. Ingatlah bahawa voltan pintu positif digunakan untuk membuat saluran pengaliran. Ia melakukan ini dengan menarik elektron. Voltan longkang positif melakukan perkara yang sama. Apabila kita menghampiri saluran longkang saluran, voltan yang membuat saluran itu semakin dekat vGS-vDS kerana kedua-dua sumber menentang satu sama lain. Apabila perbezaan ini kurang daripada VT, saluran itu tidak lagi wujud untuk keseluruhan ruang antara sumber dan longkang. Saluran itu dikekang di akhir longkang, dan peningkatan selanjutnya dalam vDS tidak menyebabkan sebarang kenaikan iD. Ini dikenali sebagai kawasan operasi normal atau tepu rantau yang ditunjukkan dalam Rajah 7 oleh seksyen mendatar kurva ciri. Apabila perbezaannya lebih besar daripada VT, kami panggil ini triode mod, kerana potensi di tiga terminal sangat mempengaruhi arus.

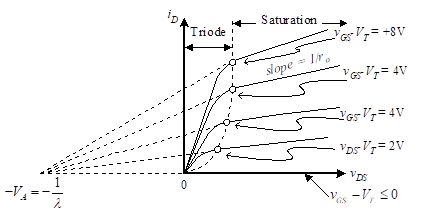

Perbincangan sebelumnya membawa kepada lengkung operasi Rajah 7.

Rajah 7 -iD berbanding vGS untuk MOSFET mod peningkatan

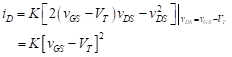

Peralihan di antara triod dan rantau operasi normal (dirujuk sebagai kawasan tepu dan sering dikenalpasti sebagai operasi dalam mode pinch-off) operasi ditunjukkan sebagai garis putus-putus dalam Rajah 7, di mana

![]()

(1)

Di sempadan kawasan triode, lutut lengkung kira-kira mengikut hubungan,

![]()

(2)

Dalam Persamaan (2), K adalah malar untuk peranti tertentu. Nilainya bergantung kepada dimensi peranti dan bahan yang digunakan dalam pembinaannya. Pemalar diberikan oleh,

![]()

(3)

Dalam persamaan ini, μn adalah mobiliti elektron; Coksida, kapasitans oksida, adalah kapasitans per unit kawasan pintu pagar; W adalah lebar pintu pagar; L adalah panjang pintu. Persamaan menunjukkan hubungan rumit dan tidak linear antara iD dan kedua-dua tegasan, vDS and vGS. Kerana kita ingin mengalir arus untuk berubah secara linear dengan kira-kira vGS (bebas daripada vDS), FET tidak digunakan secara umum di rantau triode.

Sekarang kita ingin mencari persamaan bagi lengkung operasi di kawasan tepu. Kita boleh menentukan nilai pada peralihan di antara kawasan triod dan tepu dengan menilai Persamaan (2) pada peralihan (lutut). Itu dia,

(4)

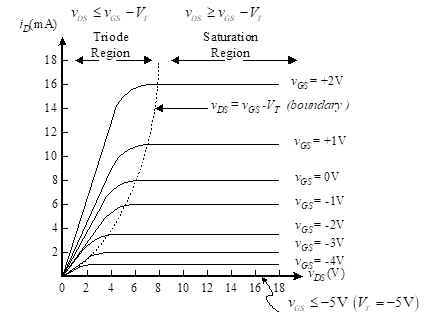

Persamaan ini menetapkan magnitud arus saliran di sempadan (garis putus-putus dalam Rajah 8) sebagai fungsi voltan pintu-ke-sumber vGS. Sekiranya perlu, kita boleh menyenaraikan lengkung sedikit ciri-ciri lengkung di kawasan tepu dengan menambahkan faktor linier.

![]()

(5)

Dalam Persamaan (5), λ adalah pemalar kecil (cerun bahagian mendatar berhampiran lengkung ciri yang ditunjukkan dalam Rajah 8). Ia biasanya kurang daripada 0.001 (V-1). Kemudian

![]()

(6)

Semua perbincangan kami sebelum ini berurusan dengan transistor NMOS. Kami kini membincangkan secara ringkas perubahan yang diperlukan untuk PMOS. Bagi PMOS, nilai - nilai vDS akan menjadi negatif. Di samping itu, untuk membuat saluran dalam PMOS, ![]() .

.

Rajah 8 - Ciri terminal transistor MOSFET

Satu-satunya perubahan dari ciri-ciri transistor NMOS (Rajah 7) ialah paksi mendatar kini -vDS bukannya + vDS, dan lengkung parametrik mewakili paras saliran yang lebih tinggi apabila voltan pintu berkurangan (bukan peningkatan untuk transistor NMOS). Kurva untuk meningkatkan nilai semasa sepadan dengan lebih banyak voltan pintu negatif. Bila vGS > VT, transistor dipotong. Untuk penambahbaikan PMOS, VT adalah negatif, dan untuk penipuan PMOS, VT adalah positif.

Persamaan untuk arus di peralihan kawasan triode untuk transistor PMOS adalah sama dengan NMOS. Itu dia,

![]()

(7)

Perhatikan bahawa vGS and vDS adalah kuantiti negatif. Persamaan untuk kawasan tepu di transistor PMOS juga sama dengan NMOS. Itu dia,

(8)

Perhatikan bahawa λ adalah negatif untuk transistor PMOS sejak kadar perubahan lengkung (![]() ) adalah negatif.

) adalah negatif.

Mengambil derivatif separa kedua-dua belah Persamaan (6) berkenaan dengan vGS, ![]() , kita mendapatkan

, kita mendapatkan

![]()

(9)

Kami lebih suka nilai gm untuk menjadi malar, terutamanya untuk perubahan isyarat yang besar. Walau bagaimanapun, kami hanya boleh menganggarkan keadaan ini jika kami menggunakan FET untuk aplikasi isyarat kecil. Untuk keadaan isyarat yang besar, penyelewengan bentuk gelombang mungkin tidak dapat diterima dalam sesetengah aplikasi.

Mod MOSFET Pengurangan 2.2

Bahagian sebelumnya menangani mod peningkatan MOSFET. Sekarang kita membezakannya dengan MOSFET mod-penipisan. Untuk nmod peningkatan saluran, untuk memperoleh saluran yang kami terpaksa menggunakan voltan positif di pintu masuk. Voltan ini harus cukup besar untuk memaksa bilangan elektron bergerak yang mencukupi untuk menghasilkan arus dalam saluran teraruh.

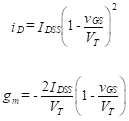

Rajah 9 - MOSFET n-channel mod pengurangan

Dalam n-MOSFET mod penipisan saluran, kita tidak memerlukan voltan positif ini kerana kita mempunyai saluran yang ditanam secara fizikal. Ini membolehkan kita mempunyai arus antara terminal longkang dan sumber walaupun dengan voltan negatif yang dikenakan pada pintu. Sudah tentu, ada had untuk jumlah voltan negatif yang dapat diterapkan ke gerbang sementara masih mempunyai aliran arus antara longkang dan sumber. Had ini sekali lagi dikenali sebagai voltan ambang, VT. Perubahan dari mod peningkatan adalah bahawa voltan pintu-ke-sumber sekarang boleh menjadi negatif atau positif, seperti yang ditunjukkan pada Gambar 9.

Persamaan-persamaan yang menentukan operasi MOSFET kekurangan mod adalah sangat serupa dengan mod peningkatan. Nilai semasa saliran apabila vGS adalah sifar dikenalpasti sebagai IDSS. Ini sering disebut sebagai aliran tepu-sumber semasa, Atau sifar - arus longkang pintu. Membandingkan persamaan MOSFET mod peningkatan dengan mod kekurangan, kita dapati

![]()

(10)

Kami kemudiannya mendapati,

(11)

MOSFET mod pengguguran boleh didapati dalam bentuk diskret, atau mereka boleh dibuat pada cip litar bersepadu tepat berserta dengan jenis mod peningkatan. Ini termasuk kedua-duanya p-tipe dan n-tipe. Ini membolehkan lebih banyak fleksibiliti dalam teknik rekabentuk litar.

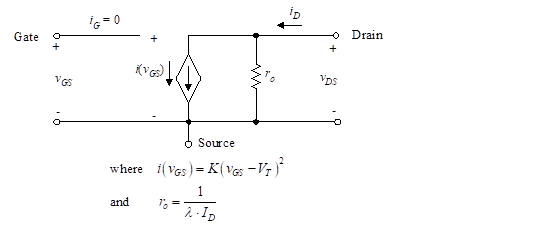

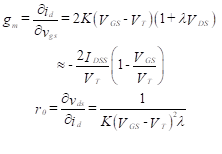

2.3 Litar bersamaan isyarat besar

Sekarang kita ingin membangunkan litar setaraf yang mewakili ciri-ciri isyarat besar Rajah 8 [Persamaan (5) atau (8)] di kawasan tepu. Perhatikan bahawa semasa saliran, iD, bergantung kepada vGS and vDS. Untuk voltan pintu-ke-sumber yang berterusan, kami beroperasi di salah satu lengkung parametrik angka, dan hubungannya adalah garis lurus yang hampir. Hubungan garis lurus antara arus dan voltan dimodelkan oleh perintang. Oleh itu litar setara terdiri daripada perintang yang selari dengan sumber arus di mana nilai sumber arus menentukan bahagian arus saliran kerana vGS. Cerun kurva bergantung kepada vGS. Cerun adalah derivatif separa,

![]()

(12)

di mana r0 adalah rintangan output tambahan. Kita lihat dari Persamaan [(5) atau (8)] bahawa rintangan ini diberikan oleh

![]()

(13)

di mana kita menggunakan huruf besar VGS untuk menunjukkan bahawa rintangan ditakrifkan untuk nilai pemalar tertentu voltan gate-to-source. Anggaran akhir dalam Persamaan (13) hasil daripada Persamaan (5) dengan andaian itu λ adalah kecil. Oleh itu, rintangan berkadar songsang dengan arus bias, ID. Model bersamaan isyarat besar kemudian diberikan oleh Rajah 11 di mana r0 adalah seperti yang dikembangkan dalam Persamaan (13).

Rajah 11 - litar bersamaan isyarat besar

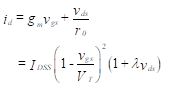

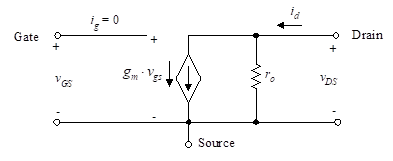

2.4 Model Isyarat Kecil MOSFET

Kami kini ingin melihat kesan tambahan yang berkaitan dengan Persamaan. Ketiga parameter litar dalam persamaan itu, iD, vGS and vDS terdiri daripada kedua-duanya dc (bias) dan ac komponen (itulah sebabnya kita menggunakan subskrip huruf besar dalam ungkapan). Kami berminat dengan ac komponen untuk model isyarat kecil. Kita melihat bahawa arus longkang bergantung kepada dua tegasan, pintu masuk ke sumber dan saliran-ke-sumber. Untuk nilai tambahan, kita boleh menulis hubungan ini sebagai

(14)

Dalam Persamaan (14), gm is transkonduktans hadapan and r0 adalah rintangan output. Nilai-nilai mereka didapati dengan mengambil derivatif separa dalam Persamaan (5). Oleh itu,

(15)

Penghampiran dalam Persamaan (15) hasil dari pemerhatian itu λ jika kecil. Persamaan (14) membawa kepada model isyarat kecil Rajah 12.

Rajah 12 - Model MOSFET isyarat kecil

SEMASA - 2. Logam-oksida Semikonduktor FET (MOSFET)

SEMASA - 2. Logam-oksida Semikonduktor FET (MOSFET) PREVIOUS- 1. Kelebihan dan Kekurangan FET

PREVIOUS- 1. Kelebihan dan Kekurangan FET