SystemC SIMULACIJA

SystemC SIMULACIJA

- Verilog-A & AMS Simulacija

- Simulacija SystemVerilog

- Verilog Simulation

- Simulacija VHDL

- VHDL-AMS simulacija

SystemC je še eno odlično orodje za modeliranje strojne opreme. Vključuje vse funkcije C ++, ki se uporabljajo po vsem svetu, in knjižnico razredov C ++, ki je posebej zasnovana za načrtovanje sistema. SystemC ima odprto kodno izvedbo in jo lahko prevedete v zelo učinkovito izvršljivo binarno kodo s prevajalnikom Microsoft Visual C ++ Visual C ++ Community. V SystemC lahko model strojne opreme na višji ravni abstrakcije kot v drugih HDL in tako za modeliranje nekaterih zelo zapleteno strojno opremo, npr mikrokontrolerji je bolj enostavno in učinkovito za uporabo kot drugi HDLs, kot VHDL ali Verilog.

V v11 in novejših različicah TINA lahko izdelujete in uporabljate komponente, modelirane v SystemC, tako v TINA-ju kot v TINACloud-u. V nadaljevanju so navedene zahteve za uporabo SystemC s TINA.

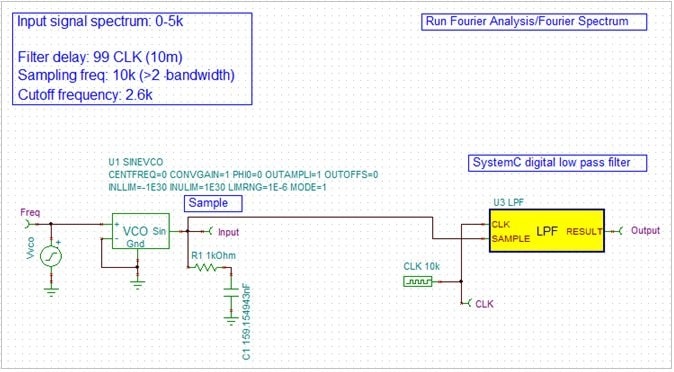

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

Lastnosti filtra in C-koda je zasnovana z brezplačnim orodjem pri

http://t-filter.engineerjs.com/

Ustvarjena C-koda je bila postavljena v datoteko fir.cpp.

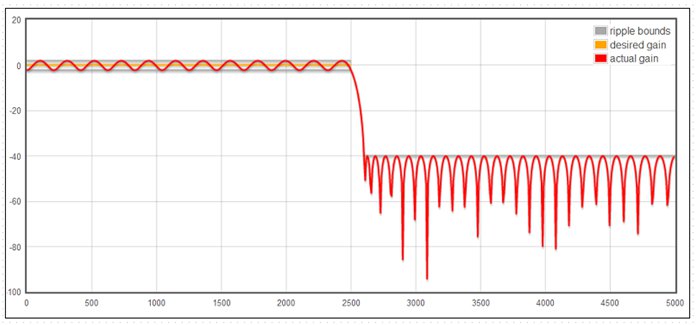

Analiza teka / Fourierova analiza / Fourierjev spekter ...

Pritisnite

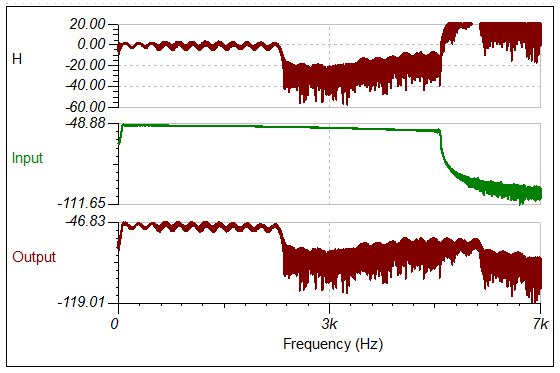

Pritisnite Več gumb. Vrsta Izhodi / vhodi / vnosi v vrstici Uredi. Vnesite H v novo ime funkcije. Pritisnite ustvarjanje. Pritisnite OK. Izberite Pogled / ločene krivulje.

Rezultat je naslednji

Najpomembnejši del makroa SystemC:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.