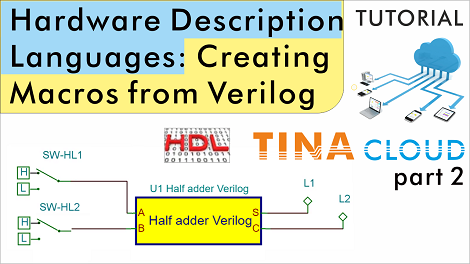

In this tutorial video we will show you how you can create a macro from a Verilog (.v) code and use in TINACloud.

You can create macros from VHDL, Verilog-A and Verilog-AMS files in a similar way.

The essential Verilog code of the half adder is 2 lines long only. The Verilog code is much simpler than the equivalent VHDL code. This is one of the great advantages of Verilog.

Similarly to our previous video “Creating Macros from VHDL” we will represent how you can turn the uploaded Verilog file into a Verilog macro. and we demonstrate how to Edit the Macro Input and Output pin names.

If you wish you can move the pin names to the top or to the bottom fields of the editor you can create pins at the top or at the bottom of the macro box.

Of course you can also change the names, for example A to Inp A, B to Inp B and so on.

Finally we will test our newly created macro in TINACloud’s Digital interactive mode along with the previously created VHDL macro and compare the results with the Truth Table of the Half Adder.

Watch our tutorial video to learn more.

You can learn more about TINA here: www.tina.com

You can learn more about TINACloud here: www.tinacloud.com