SystemC SIMULERING

SystemC SIMULERING

- Verilog-A & AMS-simulering

- SystemVerilog Simulering

- Verilog Simulering

- VHDL Simulering

- VHDL-AMS Simulering

SystemC er et annet flott verktøy for modellering av maskinvare. Den inneholder alle funksjonene til C ++, brukt over hele verden, og et C ++ klassebibliotek spesielt designet for systemdesign. SystemC har en åpen kildekodefri implementering, og du kan kompilere den til en svært effektiv kjørbar binær kode med den gratis Visual Studio Community C ++-kompilatoren fra Microsoft. I SystemC kan du modellere maskinvare på et høyere abstraksjonsnivå enn i andre HDLer, og for modellering av svært komplisert maskinvare, for eksempel mikrokontroller, er det enklere og mer effektivt å bruke enn andre HDLer som VHDL eller Verilog.

I v11 og senere versjoner av TINA kan du også lage og bruke komponenter modellert i SystemC både i TINA og TINACloud. Følgende er kravene til å bruke SystemC med TINA.

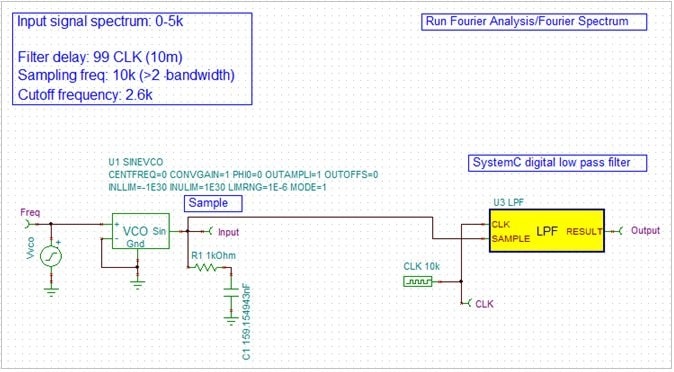

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

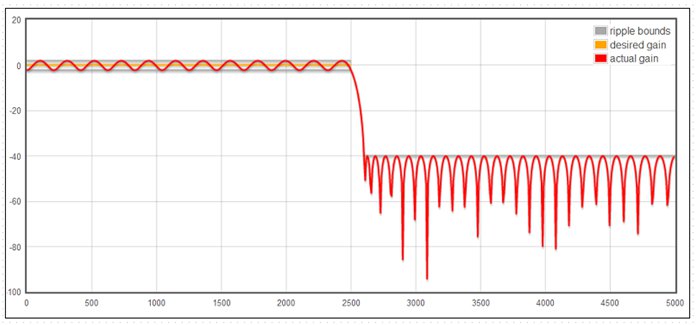

Filteregenskapene og C-koden er designet av det gratis verktøyet på

http://t-filter.engineerjs.com/

Den genererte C-koden ble plassert i fir.cpp-filen.

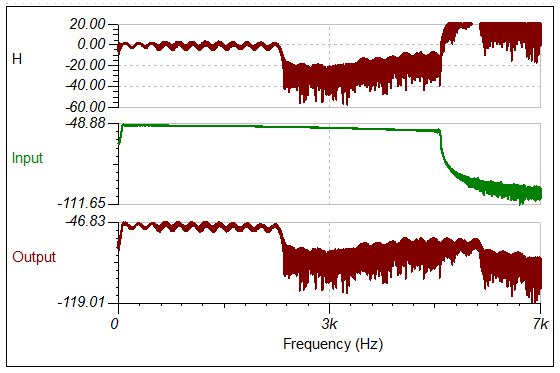

Kjør analyse / Fourier Analyse / Fourier Spectrum ...

Trykk på

Trykk på Mer knapp. Type Utgangen (e) / inngang (r) i linjebutikken. Skriv H i det nye funksjonsnavnet. trykk Opprett. trykk OK. Velg Se / Separate kurver.

Resultatet er følgende

Den viktigste delen av SystemC-makroen:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.