7. 비 반전 증폭기

비 반전 증폭기

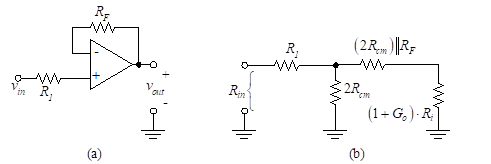

그림 29 – 비 반전 증폭기

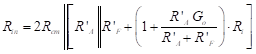

그림 29 (a)는 비 반전 증폭기, 그림 29 (b)는 등가 회로를 보여줍니다.

입력 전압은 R1 비 반전 단자에 연결합니다.

7.1 입력 및 출력 저항

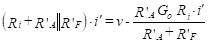

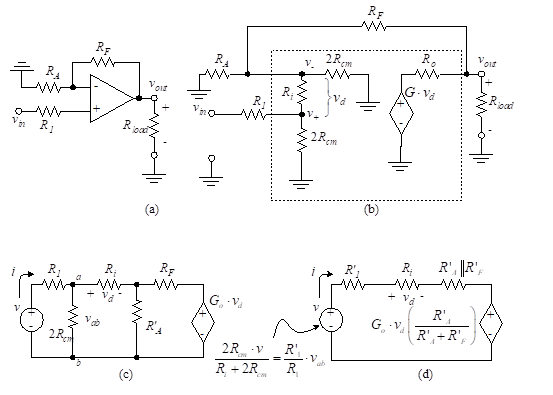

XNUMXD덴탈의 입력 저항 이 증폭기의 Thevenin은 입력 회로의 Thevenin 등가물을 결정함으로써 발견됩니다. 부하 저항은 일반적으로 R하중 >> Ro. 이것이 사실이 아니라면, 실질적인 이득은 감소 될 것이고, Ro 의 병렬 조합이 될 것이다. Ro 과 R하중. 다시 정의하고 아르 자형'F = RF + Ro. 우리는 방치 할 것이다. R1, 그것보다 훨씬 적기 때문에 Rin. 지금부터 R하중 >> Ro, 그림 29 (a)를 그림 30 (a)의 단순화 된 형식으로 줄일 수 있습니다.

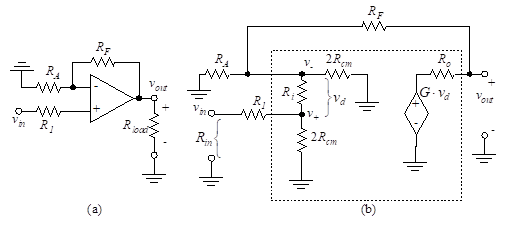

그림 30 – 입력 저항 감소 회로

우리는 Thevenin이 타원 곡선으로 둘러싸여있는 회로를 찾음으로써 그림 30 (b)를 얻습니다. 그림 30 (c)에서 2의 오른쪽에 대한 저항Rcm ~에 의해 주어진다. v/나는'. 이를 평가하기 위해 루프 방정식을 작성하여

(53)

따라서,

(54)

입력 저항은이 양과 2의 병렬 조합입니다Rcm.

(55)

리콜, 아르 자형'F = RF + Ro및 R하중 >> Ro. 우리가 가장 중요한 용어만을 사용하고 Rcm 가 크면 방정식 (55)은

(56)

여기서 우리는 다시 제로 주파수 전압 이득을 사용하는데, Go.

방정식 (56)은 741 연산 증폭기의 입력 저항을 찾는 데 사용할 수 있습니다. 표 1에 주어진 매개 변수 값을 대입하면 식 (56)는

![]()

우리는 다시 가정을 사용합니다. Rcm 크다. 아르 자형'F » RF 과 아르 자형'A » RA. 그러면 741 연산 증폭기의 출력 저항은

(57)

예

그림 31 (a)에 표시된 단일 이득 팔로워의 입력 저항을 계산합니다.

해결 방법 : 등가 회로는 그림 31 (b)에 나와 있습니다. 우리는 제로 주파수 이득을 가정하기 때문에, Go, 공통 모드 저항, Rcm, 높다, 우리는 그 용어를 소홀히 할 수있다. ![]() (1 +Go)Ri. 방정식 (57)은 이후로 사용할 수 없습니다. RA = 0. 입력 저항은 다음과 같이 주어진다.

(1 +Go)Ri. 방정식 (57)은 이후로 사용할 수 없습니다. RA = 0. 입력 저항은 다음과 같이 주어진다.

이것은 일반적으로 400 MΩ 이상이므로 무시할 수 있습니다. R1 (즉, 집합 R1 = 0).

7.2 전압 이득

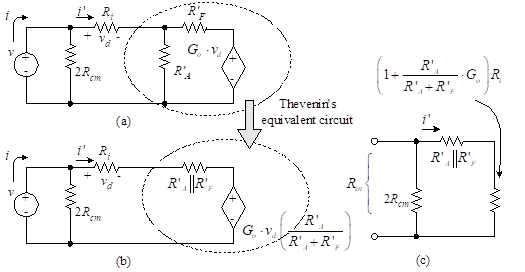

전압 이득을 결정하고, A+ 그림 32 (a)의 비 반전 증폭기의 경우.

그림 32 - 비 반전 증폭기

이 이득은 다음과 같이 정의됩니다.

(58)

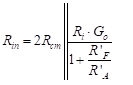

등가 회로는 그림 32 (b)에 나와 있습니다. 우리가 가정한다면 RF>>Ro, R하중>>Ro 회로는 그림 32 (c)에 표시된 것까지 줄일 수 있습니다. 추가로 정의하면 그림 32 (d)가 결과로 나타납니다.

가정 된 조건은 유효 이득의 감소를 방지하기 위해 바람직하다. Thevenin 등가물을 취하는 동작은 그림 32 (d)에서와 같이 종속 전압 소스와 구동 전압 소스를 수정합니다. 유의 사항

(59)

출력 전압은

(60)

우리는 찾을 수있다. i 그림 32 (d)의 회로에 KVL을 적용하여

(61)

(62)

어디에

과 ![]() 암시하는

암시하는 ![]() .

.

현재, i, 우리는

(63)

전압 이득은 입력 전압 대 출력의 비율로 나타냅니다.

(64)

이 결과를 확인하기 위해 이상적인 연산 증폭기의 모델로 줄일 수 있습니다. 우리는 제로 주파수 이득을 사용하는데, Go, 대신에 G (64) 및 다음 동등성에 따라 결정됩니다.

(65)

우리가 ![]() , 방정식 (64)은 다음과 같이됩니다.

, 방정식 (64)은 다음과 같이됩니다.

(66)

이상화 된 모델에 대한 결과와 일치합니다.

예

그림 33에 표시된 단일 이득 추종자의 이득을 찾습니다.

그림 33 - 통합 이득 추종자해결 방법 : 이 회로에서, ![]() , 아르 자형'A = 2Rcm및 RF << 아르 자형'A. 우리는 Go 큰,

, 아르 자형'A = 2Rcm및 RF << 아르 자형'A. 우리는 Go 큰, ![]() , 우리는 R1 = RF. 방정식 (64)는 다음으로 감소합니다.

, 우리는 R1 = RF. 방정식 (64)는 다음으로 감소합니다.

(67)

so v아웃 = vin 예상대로

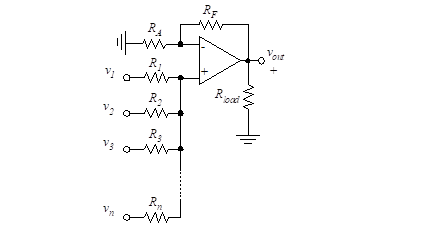

7.3 다중 입력 증폭기

이전의 결과는 다중 전압 입력을 갖는 비 반전 증폭기의 경우까지 확장된다. 그림 34은 다중 입력 비 반전 증폭기를 보여줍니다.

그림 34 - 다중 입력 비 반전 증폭기

입력 v1, v2, v3,…, vn 입력 저항을 통해 적용된다. R1, R2, R3,…, Rn, 우리는 다음과 같이“이상적인 연산 증폭기”장에서 파생 된 일반적인 결과의 특별한 경우를 얻습니다.

(68)

우리는 선택합니다

(69)

바이어스 균형을 달성한다. 출력 저항은 식 (52)에서 구합니다.

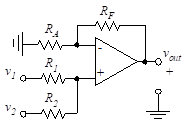

구체적인 예로서 그림 35의 2 입력 합산 기의 출력 전압을 결정합시다.

(35)

출력 전압은 다음과 같이 식 (68)에서 구할 수 있습니다.

(70)

우리는 선택합니다 ![]() 바이어스 균형을 달성한다. 우리가 가정한다면 RF = R1 = R2 = RA, 방정식 (70)은 v아웃 = v1 + v2, 이것은 단일성 이득 2 - 입력 여름이다.

바이어스 균형을 달성한다. 우리가 가정한다면 RF = R1 = R2 = RA, 방정식 (70)은 v아웃 = v1 + v2, 이것은 단일성 이득 2 - 입력 여름이다.

CURRENT – 7. 비 반전 증폭기

CURRENT – 7. 비 반전 증폭기 이전 - 6. 연산 증폭기 회로의 컴퓨터 시뮬레이션

이전 - 6. 연산 증폭기 회로의 컴퓨터 시뮬레이션