3. 일반 Op 앰프

일반 Op 앰프

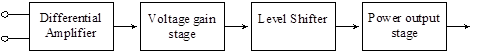

대부분의 연산 증폭기는 그림 8에 표시된 블록 다이어그램에 따라 설계 및 제작됩니다.

그림 8 - 연산 증폭기의 일반적인 구성

차동 증폭기와 전압 이득 단은 전압 이득을 제공하는 유일한 단이다. 차동 증폭기는 또한 연산 증폭기에서 매우 중요한 CMRR을 제공한다. 차동 증폭기의 출력은 종종 높은 이미 터 저항을 갖는 이미 터 종 동자 (emitter follower)에 연결되어 높은 이득을 얻기 위해 차동 증폭기에 고 임피던스 부하를 제공합니다. 하이 게인 공통 이미 터 앰프는 적당한 게인 CE 앰프보다 훨씬 낮은 입력 임피던스를 가지고 있다는 것을 기억하십시오. 이렇게하면 추가 게인을 제공하기 위해 고 이득 CE 증폭기를 사용할 수 있습니다. 선형 op 앰프는 ac 이득. 이는 또한 IC 칩 상에 위치하기에 너무 큰 커플 링 커패시터에 대한 필요성을 제거한다. 레벨 쉬프터는 출력 신호에 dc 오프셋. 연산 증폭기는 회로 시뮬레이션을 통해 매우 정확하게 모델링 할 수 있습니다. TINACloud 온라인 회로 시뮬레이션을 사용하여이를 시연합니다.

3.1 패키징

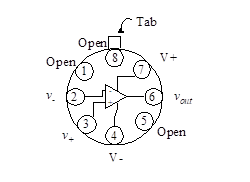

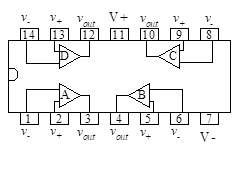

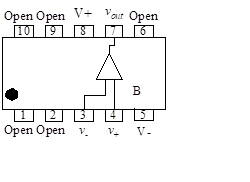

연산 증폭기 회로는 캔, DIP (듀얼 인라인 패키지) 및 플랫 팩을 포함한 표준 IC 패키지로 제공됩니다. 이들 각각의 패키지는 적어도 8 개의 핀 또는 연결부를 갖는다. 그림 9, 10 및 11에 그림이 나와 있습니다.

그림 9 - 캔 패키지를위한 Op 앰프 연결 (평면도)

그림 10 – 연산 증폭기 연결 14 핀 DIP (상단 모습)

그림 11 - 10 핀 플랫 팩을위한 Op 앰프 연결 (상단보기)

회로를 만들 때 다양한 리드를 올바르게 식별하는 것이 중요합니다 (일반적으로 번호가 매겨지지 않음). 그림은 핀 1의 위치를 보여줍니다. 에서 깡통 포장 그림 9의 1 핀은 탭 왼쪽의 첫 번째 핀으로 식별되며, 핀은 위로부터 시계 반대 방향으로 연속적으로 번호가 매겨집니다. 에서 듀얼 인라인 패키지 그림 10의 패키지 상단에는 핀 1을 찾기위한 들여 쓰기가 있고 핀은 왼쪽과 오른쪽에 번호가 매겨져 있습니다. 하나의 DIP에는 하나 이상의 연산 증폭기 (일반적으로 2 또는 4)가 패키지되어 있습니다.

. 편평한 팩 그림 11의 1 핀은 점으로 식별되며 핀은 DIP에서와 같이 번호가 매겨집니다.

3.2 전원 요구 사항

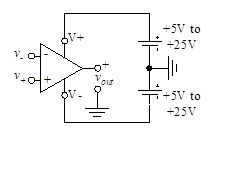

많은 op-amp에는 음 전압 및 양 전압 소스가 모두 필요합니다. 일반적인 전압 소스의 범위는 ± 5 V ~ ± 25 V입니다. 그림 12는 op-amp에 대한 일반적인 전원 공급 장치 연결을 보여줍니다.

최대 출력 전압 스윙은 dc 연산 증폭기에 공급되는 전압. 일부 연산 증폭기는 단일 전압 소스에서 작동 할 수 있습니다. 제조업체의 사양은 연산 증폭기가 하나의 전원 공급 장치 만 사용하는 경우 작동 제한을 정의합니다.

그림 12 - 전원 공급 장치 연결부

최대 출력 전압 스윙은 dc 연산 증폭기에 공급되는 전압. 일부 연산 증폭기는 단일 전압 소스에서 작동 할 수 있습니다. 제조업체의 사양은 연산 증폭기가 하나의 전원 공급 장치 만 사용하는 경우 작동 제한을 정의합니다.

3.3 741 Op 앰프

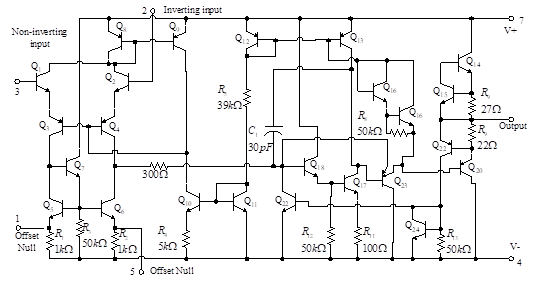

μA741 연산 증폭기는 그림 13의 등가 회로에 나와있다. 이것은 대부분의 IC 제조업체가 1966을 제작 한 이후 제작되었으며, 도입 이후 많은 발전이 있었지만 741은 여전히 널리 사용되고 있습니다.

그림 13 - 741 연산 증폭기

741 연산 증폭기는 내부 보상 이것은 고주파 진폭 응답을 떨어 뜨리는 RC 네트워크를 나타냅니다. 증폭기는 높은 이득을 갖기 때문에 (104 10로5 낮은 주파수에서) 그리고 트랜지스터의 기생 커패시턴스가 기생 피드백, 연산 증폭기가 불안정 해지고 내부 보상이 아닌 경우 발진한다. 2 개의 캐스케이드 차동 증폭기는 다른 전압 증폭기를 통해 상보 대칭 전력 증폭기를 구동한다.

741 연산 증폭기는 입력 차동 증폭기, 중간 단일 종단 고 이득 증폭기 및 출력 버퍼링 증폭기의 3 단계로 구성됩니다. 작동에 중요한 다른 회로로는 레벨 쉬프터가있다. dc 출력이 양극 및 음극으로 진동 할 수 있도록 신호의 레벨, 다양한 증폭기에 기준 전류를 제공하는 바이어스 회로 및 출력에서 단락 회로로부터 연산 증폭기를 보호하는 회로를 포함한다. 741은 온칩 커패시터 - 저항 네트워크를 통해 내부적으로 보상된다.

연산 증폭기는 더 많은 증폭 단계를 추가하고, 입력 회로를 절연하고, 출력에서 임피던스 팔로어를 더 추가하여 출력 임피던스를 감소시킴으로써 더욱 향상된다. 다른 개선 사항은 CMRR 증가, 높은 입력 임피던스, 더 넓은 주파수 응답, 감소 된 출력 임피던스 및 증가 된 전력을 초래한다.

바이어스 회로

그림 741의 13 연산 증폭기에서 여러 가지 상수원을 볼 수 있습니다. 트랜지스터 Q8 과 Q9 현재 소스 IEE 에 의해 형성된 차동 증폭기 Q1, Q2, Q3및 Q4. 트랜지스터 Q5, Q6및 Q7, 활성로드를 대체하는 활성로드 RC 차동 증폭기의 저항. 트랜지스터 Q10, Q11및 Q12 차동 증폭기 전류 소스에 대한 바이어스 네트워크를 형성합니다. 트랜지스터 Q10 과 Q11 전류 미러 (current mirror)로서 작용하는 다른 트랜지스터들로이 바이어스 네트워크를위한 와이드 라 (Widlar) 전류 소스를 형성한다.

단락 회로 보호

741 회로는 정상적으로 차단되고 출력에 큰 전류가 존재하는 경우에만 전도되는 다수의 트랜지스터를 포함합니다. 그런 다음 출력 트랜지스터의 바이어스를 변경하여이 전류를 수용 가능한 수준으로 줄입니다. 그림 13의 회로에서이 단락 보호 네트워크는 트랜지스터 Q15 과 Q22 저항기 R11.

입력 단계

741 연산 증폭기의 입력 스테이지는 전압 이득, 레벨 시프 팅 및 단일 종단 차동 증폭기 출력을 제공해야한다. 회로의 복잡성으로 인해 큰 오프셋 전압 오류가 발생합니다. 이와 달리 표준 저항 부하 차동 증폭기는 오프셋 전압 오류를 줄입니다. 그러나 표준 증폭기는 이득이 제한되어있어 원하는 증폭을 달성하기 위해 더 많은 단계가 필요합니다. 저항 부하 차동 증폭기는 741보다 전압 편차가 적은 연산 증폭기에 사용된다.

입력 단계에서 사용되는 BJT는 큰 바이어스 전류를 필요로하므로 오프셋 전류 문제가 발생한다. 오프셋 전류 오류를 줄이기 위해 다른 op 앰프 유형은 입력 단계에서 MOSFET을 사용한다.

741의 입력 스테이지는 트랜지스터에 의해 형성되는 능동 부하를 갖는 차동 증폭기입니다 Q5, Q6및 Q7 및 저항기 R1, R2및 R3. 이 회로는 높은 저항 부하를 제공하고 이득 또는 공통 모드 제거비의 저하없이 차동 신호를 단일 종단 형 신호로 변환합니다. 단일 종단 형 출력은 Q6. 입력 스테이지 레벨 시프터는 측면 PNP 트랜지스터들, Q3 과 Q4이들은 공통 기본 구성으로 연결됩니다.

측면 트랜지스터의 사용, Q3 과 Q4, 장점이 추가됩니다. 이들은 입력 트랜지스터 보호, Q1 과 Q2에미 터 -베이스 접합 파괴에 대해 에미 터 -베이스 접합은 npn 트랜지스터는 역 바이어스가 약 7 V를 초과하면 파괴 될 것이다. 횡 방향 트랜지스터 브레이크 다운은 역 바이어스가 약 50 V를 초과 할 때까지 발생하지 않는다. 트랜지스터는 Q1 과 Q2입력 회로의 항복 전압이 증가된다.

중급 단계

대부분의 op-amp의 중간 단계는 여러 앰프를 통해 높은 이득을 제공합니다. 741에서 첫 단계의 단일 종단 출력은 Q16 이는 에미 터 팔로워 구성에있다. 이는 입력단에 높은 입력 임피던스를 제공하여 부하를 최소화합니다. 중간 단계는 또한 트랜지스터 Q16 과 Q17, 저항기 R8 과 R9. 중간 스테이지의 출력은 Q17, 제공되는 Q14 위상 스플리터를 통해 출력한다. 741의 커패시터는이 텍스트의 후속 장에서 논의되는 주파수 보상에 사용됩니다.

출력 단계

연산 증폭기의 출력 단계는 낮은 출력 임피던스에 높은 전류 이득을 제공하는 데 필요합니다. 대부분의 연산 증폭기는 보완 대칭 출력 스테이지를 사용하여 전류 이득을 희생하지 않고 효율성을 높입니다. 상보 대칭 인 클래스 B 증폭기에 대해 달성 가능한 최대 효율은 78 %입니다. 단일 종단 출력 증폭기는 최대 효율이 25 %에 불과합니다. 일부 연산 증폭기는 Darlington 쌍 상보 대칭을 사용하여 출력 기능을 향상시킵니다. 741의 보완 대칭 출력 단계는 다음으로 구성됩니다. Q14 과 Q20.

작은 저항기, R6 과 R7출력에서 전류 제한을 제공합니다. 달링턴 쌍, Q18 과 Q19는 8 장에서 설명 된 다이오드 보상 된 상보 대칭 출력 단계에서 다이오드 대신에 사용됩니다. Darlington pair 배열은 더 작은 영역에서 제작 될 수 있기 때문에 다이오드로 연결된 두 개의 트랜지스터보다 선호됩니다. 상보 적 대칭 회로의 바이어스 저항을 대신하는 전류원은 트랜지스터의 일부분 Q13. 트랜지스터 Q22, Q23및 Q24 는 출력 전압이 제로 축을 중심으로되도록 보장하는 레벨 시프터 배열의 일부입니다.

CURRENT – 3. 일반적인 연산 증폭기

CURRENT – 3. 일반적인 연산 증폭기

이전 - 2. 레벨 쉬프터

이전 - 2. 레벨 쉬프터