9. FET 증폭기 분석

FET 증폭기 분석

9.1 CS (및 소스 저항) 앰프

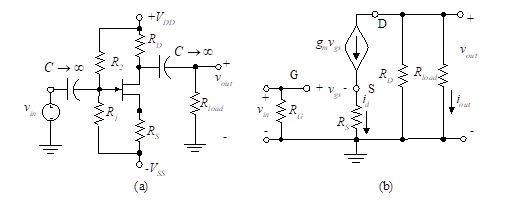

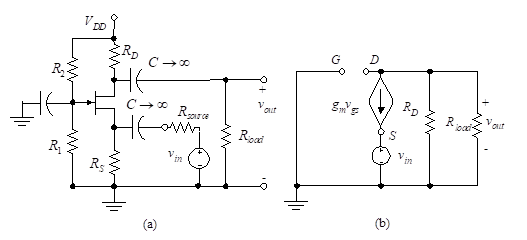

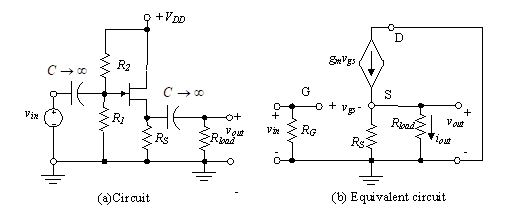

그림 33 – 소스 저항기가있는 CS 증폭기

그림 33 (a)는 소스 저항이있는 CS 증폭기를 보여준다. 그만큼 ac 등가 회로는 그림 33 (b)에있다. 우리는 추정하다 ro 에 비해서 크기가 크므로 무시 될 수 있습니다. 콘덴서가 소스와 접지 사이에 존재한다면 (즉, CS 증폭기), 간단히 설정해야합니다 RS 다음에서 0과 같다. ac 방정식. 우리는이 파생의 결론에 이것을한다.

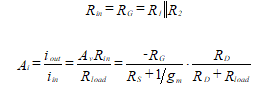

그림 33의 (b) RG 의 병렬 조합이다. R1 과 R2 과 VGG 바이어스 회로의 Thevenin 등가 전압입니다.

(41)

(41)

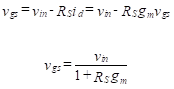

분석하려면 ac 등가 회로에서 게이트 회로 주변에 KVL 방정식을 씁니다.

(42)

(42)

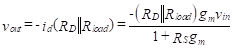

출력 전압, v아웃에 의해 주어진다.

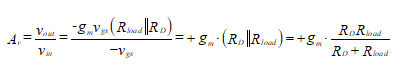

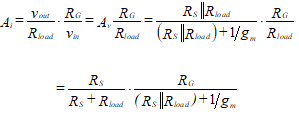

전압 이득, Av, 지금 발견된다.

(43)

(43)

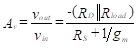

소스 저항, RS, 커패시터에 의해 바이 패싱된다. RS = 0이고, 전압 이득은

![]() (44)

(44)

일반적으로 큰 음수입니다.

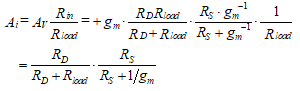

입력 저항과 전류 이득은 다음 식에 의해 주어진다.

(45)

(45)

9.2 CG 앰프

그림 37 (a)는 1 단 공통 게이트 앰프를, 그림 6.37 (b)는 ac 동등한. 우리는 다시 한 번 무시했습니다. ro 병렬 조합과 비교하여 큰 가정 RD 과 R하중.

그림 37 - CG 증폭기

그림 37 (b)에서 가장 왼쪽 루프에서 게이트 - 소스 전압은

![]() (46)

(46)

현재를 통해 RS is

(47)

(47)

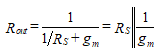

소스에서 보이는 (입력) 저항은

![]() (48)

(48)

이것은 CS 증폭기의 방정식 (45)과 비교되어야한다. 게이트 저항이 높으면 공통 소스 앰프의 입력 저항이 공통 게이트 앰프의 입력 저항보다 훨씬 클 수 있습니다. 사실 CG 증폭기의 애플리케이션 수는 입력 임피던스가 낮기 때문에 제한적입니다.

전압 이득은 다음과 같이 주어진다.

(49)

(49)

이를 방정식 (44)과 비교해 보면, 소스 회로에서 바이 패스되지 않은 저항을 갖는 CS 증폭기의 전압 이득은 CG 증폭기가 위상을 이동시키지 않는다는 점을 제외하고는 CG 증폭기의 전압 이득과 동일하다는 것을 알 수있다.

출력 저항은 RD (시험 전류를 넣고 전압을 측정하면서 설정 vin 0으로).

CG 증폭기의 현재 이득은

(50)

(50)

9.3 CD (SF) 앰프

그림 39 (a)는 1 단 공통 드레인 소스 팔로워 (SF) 증폭기를 보여주고 그림 39 (b)는 ac 동등한. 우리가 분석 한 각 구성과 마찬가지로, 우리는 큰 저항을 생략하고, ro 가정 하에서 그것은 평행 조합보다 훨씬 큽니다. RS 과 R하중.

그림 39 - CD 앰프

입력 저항은 간단합니다. Rin = RG. 게이트 - 소스 루프 주위에 KVL 방정식을 작성하면

![]() (51)

(51)

우리가 얻을 수있는

![]() (52)

(52)

출력 전압은

![]() (53)

(53)

전압 이득은 출력 대 입력 전압의 비율입니다.

![]() (54)

(54)

이 전압 이득은 1보다 작으며, 병렬 결합으로 1에 접근합니다. RS 과 R하중 증가합니다.

우리는 현재 현재 이득을 발견합니다. 출력 전류는 출력 전압과 부하 저항의 비율입니다. 입력 전류는 입력 전압을 RG. 따라서 이득은 다음과 같이 주어진다.

(55)

(55)

출력 저항은 부하 저항을 테스트 전압으로 교체하면 알 수 있습니다. vtest, 그 다음에 결과적인 전류를 찾는다. itest. 이 테스트 소스에 의해 구동되는 전류는 소스의 노드 방정식에서 발견됩니다.

![]() (56)

(56)

게이트 - 소스 간 전압은 간단히 -vtest 왜냐하면 입력 전압이 0이라고 가정하기 때문입니다. 따라서, 출력 저항은

(57)

(57)

CURRENT – 9. FET 증폭기 분석

CURRENT – 9. FET 증폭기 분석 이전 -8. FET 증폭기 – 표준 구성

이전 -8. FET 증폭기 – 표준 구성