12. 파워 오디오 Op 앰프

파워 오디오 Op 앰프

선형 증폭기의 일반적인 용도는 오디오 시스템에 이득을 제공하는 것입니다. 안 오디오 증폭기 마이크, 축음기 카트리지, 테이프 데크 또는 AM / FM 튜너로부터 입력 신호를 수신합니다. 앰프의 출력은 스피커 시스템, 헤드폰 또는 테이프 레코더를 구동합니다. 위에 명명 된 입력 장치는 일반적으로 출력 전압이 낮고 소스 임피던스가 높은 전압 소스로 모델링 할 수 있습니다. 따라서이 소자를 따르는 증폭기의 입력 임피던스는 높아야한다 (입력 소자의 소스 임피던스보다 훨씬 더 커야한다). 이러한 방식으로, 증폭기는 입력 장치에 큰 부하를주지 않으며 이득은 감소하지 않는다.

증폭기로 구동되는 디바이스는 보통 낮은 임피던스를 갖는다. 예를 들어, 단일 스피커의 임피던스는 일반적으로 8 Ω입니다. 이러한 장치는 1 ~ 10 W의 순서로 힘을 요구할 수 있습니다.

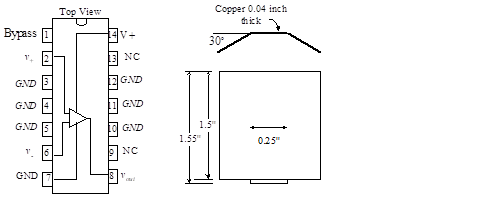

그림 48 - LM380 오디오 칩 및 선택 사양 방열판

다양한 출력 전력을 갖춘 다양한 집적 회로 오디오 전력 op 앰프를 전자 설계 엔지니어가 이용할 수있다. 예를 들어, LM380 오디오 전력 증폭기[1] 인터콤, 라인 드라이버, 알람, TV 사운드 시스템, AM / FM 라디오, 소형 서보 드라이버 및 전력 변환기와 같은 소비자 애플리케이션에 사용됩니다. 내부적으로 고정 된 50 (34 dB) 게인과 전원 전압의 절반 정도를 중심으로하는 출력이 있습니다. 입력은 접지 또는 밸런스를 기준으로 할 수 있습니다. 출력 단은 단락 전류 제한 및 열 셧다운 회로로 보호된다. 앰프는 그림 14 (a)와 같이 48 핀 DIP 패키지로 포장되어 있습니다.

출력 전류는 1.3 A 피크로 정격됩니다. 150 이상의 접합 온도에서 디바이스가 셧다운되기 때문에 oC, 히트 싱크 [그림 48 (b) 참조]를 장치에 납땜해야합니다. 최대 출력 (방열판 포함)은 3.7 와트입니다. 이 장치는 내부적으로 바이어스되어 있습니다.

1데이터와 회로는 제조업체 인 National Semiconductor Corp의 허가를 받아 인쇄됩니다. 학생은 전력 연산 증폭기가있는 장비를 설계 할 때 데이터 북을 사용해야합니다.

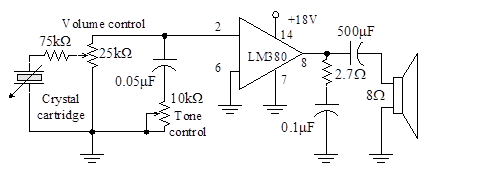

그림 49는 완전한 포노 앰프의 회로 구성을 보여줍니다. 볼륨과 톤 컨트롤이이 회로에 포함되었습니다.

그림 49 - LM380를 사용하는 포노 증폭기

12.1 연산 증폭기 등가 회로

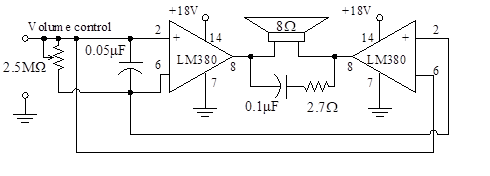

특정 애플리케이션이 단일 전력 연산 증폭기보다 많은 전력을 필요로하는 경우 그림 50의 브리지 구성을 사용할 수있다.

이 시스템은 단일 디바이스 시스템과 같이 부하에서 전압 스윙을 두 배로 제공하기 때문에 단일 전원 시스템에 비해 이론적으로 4만큼 전원 성능이 향상됩니다 (주어진 전원 전압에 대해). 이 설계에서는 열 방출이 제한적인 관심사이므로 일반적으로 시스템을 보수적으로 설계하고 출력 전력을 두 배로 늘립니다.

그림 50 - 고전력을위한 브리지 구성

인터콤 12.2

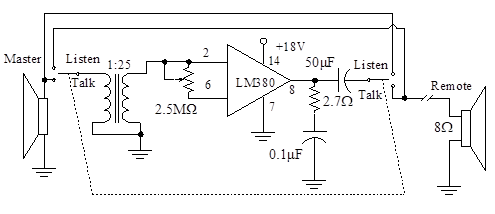

그림 51는 파워 연산 증폭기와 몇 가지 외부 부품을 통합 한 인터콤을 보여줍니다.

토크 위치에 그림과 같이 듀얼 2 포지션 스위치 (S1A-S1B)가 있으면 마스터 스테이션의 스피커가 마이크로폰의 기능을 수행하여 스텝 업 트랜스포머를 통해 파워 연산 증폭기를 구동합니다. 원격 스피커는 파워 연산 증폭기의 출력에서 구동된다.

S1A-S1B를 청취 위치로 전환하면 마스터 및 리모컨의 역할이 바뀝니다. 이제 먼 스피커는 마이크로폰 역할을하며 스텝 업 트랜스포머를 통해 전력 증폭기를 구동합니다. 이제 마스터 스피커는 파워 op 앰프의 출력에서 구동된다. 학생은 S1A-S1B가 청취 위치에 있는지 확인하기 위해 배선을 추적해야합니다. 권선비 1 : 25의 스텝 업 변압기를 사용할 수 있으며, 전위차계, Rv, 볼륨 컨트롤로 작동합니다.

그림 51 – 인터콤

개요

이 장은“이상적인 연산 증폭기”여기서 우리는 이상적인 연산 증폭기에 중점을 두었다. 이 중요한 빌딩 블록이 이상적인 증폭기로 동작하더라도 설계 엔지니어는 실제 장치와 이상적인 모델 간의 대비를 이해해야합니다.

우리는 차동 증폭기를 검사하여이 장을 시작했습니다. 다양한 구성과 전송 특성을 살펴 보았습니다. 그런 다음 패키징 및 내부 회로를 포함한 일반적인 연산 증폭기를 검사했습니다. 제조업체가 앰프에 대한 매개 변수를 지정하는 방식을 살펴 보았습니다.

이득, 오프셋 전압, 바이어스 전류, 공통 모드 제거 및 전원 공급 거부 비율을 포함한 실용적인 op 앰프의 특성이 제시되었다. 다음으로 컴퓨터 시뮬레이션 모델을 검토 한 후 비 반전 및 반전 증폭기에 대한 상세한 분석을 수행했습니다.

이 장은 다양한 설계 고려 사항과 예제로 결론 지었다. 균형 잡힌 입출력과 입력 간의 결합을 조사했습니다. 우리는 또한 인터콤 회로의 예를 포함 해 파워 오디오 op 앰프를 살펴 보았다.

----

1데이터와 회로는 제조업체 인 National Semiconductor Corp의 허가를 받아 인쇄됩니다. 학생은 전력 연산 증폭기가있는 장비를 설계 할 때 데이터 북을 사용해야합니다.

CURRENT – 12. 파워 오디오 연산 증폭기

CURRENT – 12. 파워 오디오 연산 증폭기 이전 - 11. 다중 입력 간의 결합

이전 - 11. 다중 입력 간의 결합