IBIS Simulation

IBIS Simulation

Jump to TINA Main Page & General Information

IBIS Simulation

IBIS (Specifikacija informacija ulaznog / izlaznog pufera) je metoda koja pruža informacije o modeliranju ulaznih / izlaznih bafera integriranih krugova. Dobra stvar kod IBIS modela je u tome što su oni često dostupni čak i za uređaje u kojima proizvođači ne mogu nabaviti kompletne modele uređaja iz bilo kojeg razloga (npr. Složenost, vlasnička zaštita informacija, itd.).

Jedna od najpopularnijih upotreba IBIS modela je analiza integriteta signala, uključujući usklađivanje impedancije i još mnogo toga.

TINA trenutno podržava najrašireniju verziju IBIS 4.2-a.

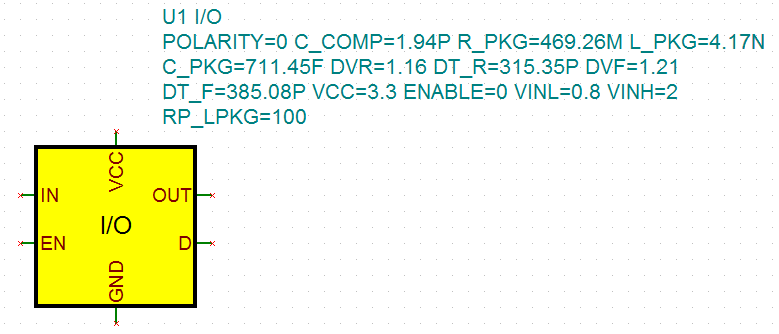

U TINA-i možete pretvoriti IBIS modele u TINA Spice makroe i onda ih koristiti u bilo kojim krugovima u TINA-i. Također možete dovršiti pojednostavljene modele digitalnih uređaja - npr. MCU s IBIS modelima - kako bi bolje opisali njihovo analogno ponašanje.

U nastavku ćemo prikazati upotrebu IBIS modela kroz primjer fiksiranja integriteta signala između Texas Instruments TMS320C6748 DSP i ADS1259 delta-sigma ADC.

izabrati Datoteka / Uvoz / IBIS datoteka (* .ibs), izaberite c6748zce.ibs od TINA directory >Primjeri IBIS.

Prikazat će se sljedeći dijalog. U ovom dijalogu možete odabrati model za uvoz.

Sada izaberite SPI1CLK_GP213 signal, PBFZP18LL_X50_PI_3P3 model (ćelija koja radi na 3.3V bez povlačenja ili padajućeg) tip value set.

Pritisnite OK. IBIS model se automatski pretvara u Spice makro.

SPI1CLK_GP213 je glavni satni signal takta TMS320C6748 čipa za pogon SPI taktnog ulaza AD konvertera, Texas Instruments ADS1259.

izabrati Datoteka / Uvoz / IBIS datoteka (* .ibs), izaberite ads1259.ibs od TINA directory >Primjeri IBIS.

Prikazat će se sljedeći dijalog. U ovom dijalogu možete odabrati model za uvoz.

Sada izaberite SCK ulazni signal, DIN_PD_3 model i maksimum vrijednost (za 3.3V DVDD naponski raspon).

Pritisnite OK. IBIS model se automatski pretvara u Spice makro.

Povežite DSP I / O bafer sa ulazom ADC-a sa prenosnom linijom bez gubitaka.

Dodajte izvor napajanja i generator napona da biste kreirali satni signal DSP strane. Postavite naponske igle za simulaciju na signalne čvorove.

Parametre transmisione linije podešavamo na nekoliko inča mikrotrakastih tragova usmjerenih na četveroslojnom PCB-u. Ovo proizvodi cc. 500ps kašnjenje i 90 Ohm karakteristična impedansa.

File from \ Primjeri \ IBIS \ Odgovarajuće impedanse TMS320C6748.TSC je spreman za upotrebu.

Sada, kliknite Analiza, Transient.

DSP prenosi SPI taktni signal gdje neusklađenost impedancije stvara refleksije. Rezultat pokazuje refleksije stvorene impedancijskim neusklađenostima u ovoj simulaciji kruga.

Na strani ADC-a (pin EoTL), napon je izvan tla i napona napajanja, što krši apsolutni maksimalni rejting digitalnog ulaza.

Da bi se izbegli ispod i nadmašili na kraju linije treba da se uskladi izlazna impedancija drajvera sa impedansom traga umetanjem otpornika između izlaza i traga.

Postavimo 100 Ω otpornik u seriju sada sa izlazom.

Ponovo pokrenite Transient Analysis i uporedite rezultate kopiranjem važnih krivulja.

Sada možemo vidjeti da je korištenje IBIS modela za razumijevanje i pronalaženje kritičnih problema sa simulacijom pomoglo u rješavanju ovog problema.