SIMULACIÓ SystemC

SIMULACIÓ SystemC

- Simulació Verilog-A i AMS

- Simulació SystemVerilog

- Simulació de Verilog

- Simulació VHDL

- Simulació VHDL-AMS

SystemC és una altra gran eina per modelar maquinari. Inclou totes les funcions de C ++, utilitzades a tot el món, i una biblioteca de classes C ++ dissenyada especialment per al disseny de sistemes. SystemC té una implementació lliure de codi obert i es pot compilar en un codi binari executable molt eficient amb el compilador C ++ de Visual Studio Community també gratuït. A SystemC podeu modelar el maquinari a un nivell d’abstracció més alt que en altres HDL i, per tant, per modelar alguns maquinaris molt complexos, per exemple, els microcontroladors, és més fàcil d’utilitzar que altres HDL com VHDL o Verilog.

A v11 i les versions posteriors de TINA també podeu crear i utilitzar components modelitzats a SystemC tant a TINA com a TINACloud. Els següents són els requisits per utilitzar SystemC amb TINA.

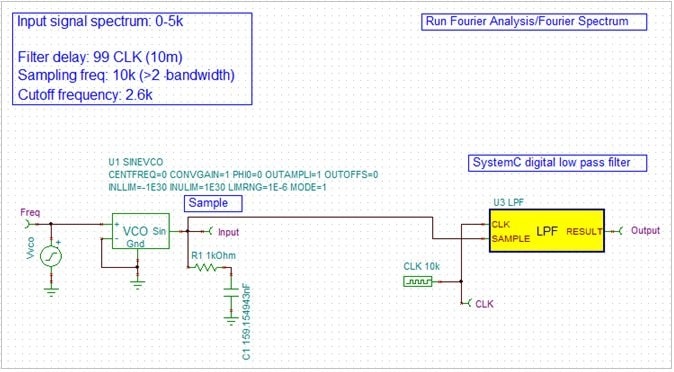

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

Les característiques del filtre i el codi C estan dissenyats per l’eina gratuïta de

http://t-filter.engineerjs.com/

El codi C generat es va col·locar al fitxer fir.cpp.

Executa l'anàlisi / anàlisi de Fourier / l'espectre de Fourier ...

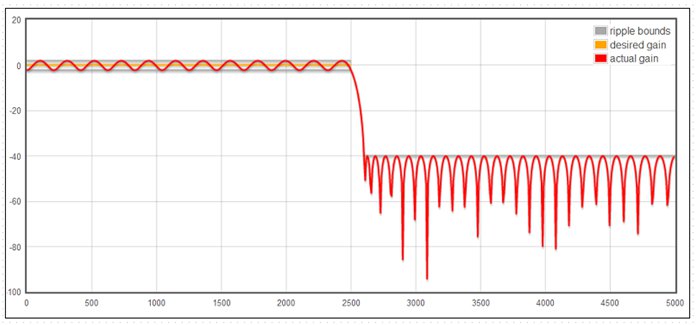

Premeu el botó

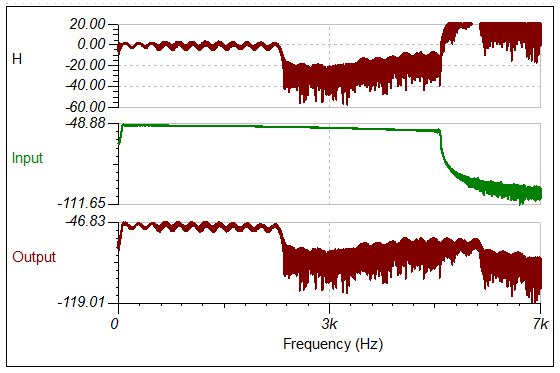

Premeu el botó més botó. Escriviu Sortida (s) / Entrada (s) a la línia d'edició. Escriviu H al nou nom de la funció. Premeu Create. Premeu OK. Seleccionar Veure / Separar corbes.

El resultat és el següent

La part més important de la macro SystemC:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.