SYMULACJA Systemu C

SYMULACJA Systemu C

- Symulacja Verilog-A i AMS

- Symulacja systemu Verilog

- Verilog Simulation

- Symulacja VHDL

- Symulacja VHDL-AMS

SystemC to kolejne świetne narzędzie do modelowania sprzętu. Zawiera wszystkie funkcje C ++, używane na całym świecie, oraz bibliotekę klas C ++ specjalnie zaprojektowaną do projektowania systemu. SystemC ma darmową implementację typu open-source i możesz skompilować ją w bardzo wydajny wykonywalny kod binarny za pomocą darmowego kompilatora Microsoft Visual Studio Community C ++. W SystemC można modelować sprzęt na wyższym poziomie abstrakcji niż w innych HDL, a więc do modelowania bardzo złożonego sprzętu, np. Mikrokontrolerów, łatwiej i wydajniej jest używać niż inne HDL, takie jak VHDL lub Verilog.

W V11 i nowszych wersjach TINA można również tworzyć i używać komponentów modelowanych w SystemC zarówno w TINA, jak i TINACloud. Poniżej przedstawiono wymagania dotyczące używania SystemC z TINA.

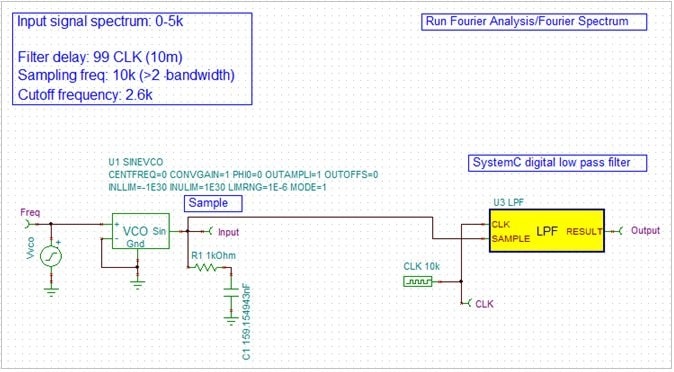

Low-pass filter example

Open the ExamplesSystemCsc lpf.TSC example.

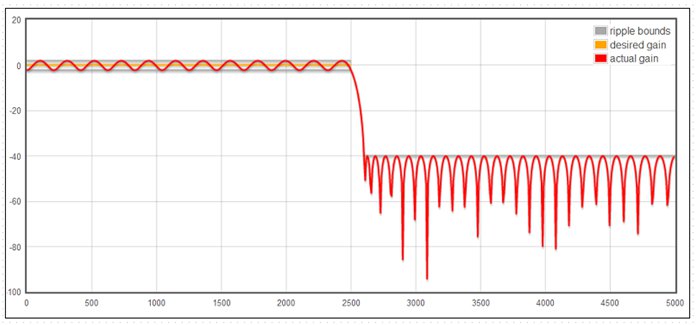

Charakterystyka filtra i kod C zostały zaprojektowane przez bezpłatne narzędzie na stronie

http://t-filter.engineerjs.com/

Wygenerowany kod C został umieszczony w pliku fir.cpp.

Uruchom analizę / analizę Fouriera / widmo Fouriera…

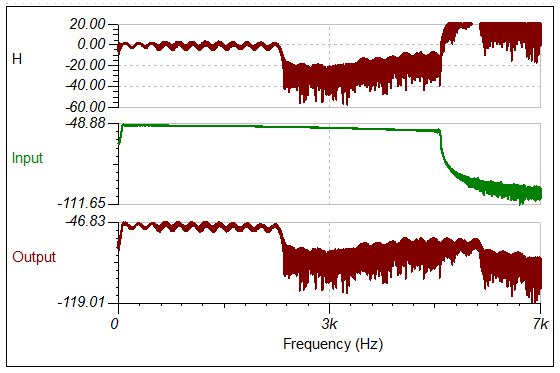

Naciśnij

Naciśnij Więcej przycisk. Rodzaj Wyjścia / wejścia / wejścia w edycji linii. Wpisz H w nazwę nowej funkcji. naciśnij Stwórz. naciśnij OK. Wybierać Zobacz / Oddzielne krzywe.

Wynik jest następujący

Najważniejsza część makra SystemC:

void fir::proc()

{

double u, y;

if (CLK.read() == SC_LOGIC_1) {

sc_logic sc_val;

// CALC

x[0] = SAMPLE; y = 0;

for (int k=0; k < M; k++){

y += b[k]*x[k];

}

// SHIFT

for (int k=M-1; k>=1; k—)

x[k] = x[k-1];

// SET VALUE

RESULT = y;

n++;

}

}

You can find this example in the Examples/Fir folder of the systemc_model.zip.